## DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

## EC3462 – LINEAR INTEGRATED CIRCUITS LAB LAB MANUAL

# II - YEAR IV SEM ECE ACADEMIC YEAR:2021-2025

| NAME     | :        |

|----------|----------|

| ROLL NO. | :        |

| REG NO.  | <b>:</b> |

| YEAR     | :        |

| SECTION  | :        |

| JEPPIAAR ENGINEERING COLLEGE |         |                                                                                                                                                                                                       |  |  |  |

|------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Vision of the Institute      | academ  | To build Jeppiaar Engineering College as an institution of academic excellence in technological and management education to become a world class University                                           |  |  |  |

|                              | M1      | To excel in teaching and learning, research and innovation by promoting the principles of scientific analysis and creative thinking                                                                   |  |  |  |

|                              | M2      | To participate in the production, development and dissemination of knowledge and interact with national and international communities.                                                                |  |  |  |

| Mission of the Institute     | М3      | To equip students with values, ethics and life skills<br>needed to enrich their lives and enable them to<br>meaningfully contribute to the progress of society                                        |  |  |  |

|                              | M4      | To prepare students for higher studies and lifelong learning, enrich them with the practical and entrepreneurial skills necessary to excel as future professionals and contribute to Nation's economy |  |  |  |

|                              |         | NT: ELECTRONICS AND CATION ENGINEERING                                                                                                                                                                |  |  |  |

| Vision of the Department     | produce | ome a centre of excellence to provide quality education and e creative engineers in the field of Electronics and unication Engineering to excel at international level.                               |  |  |  |

|                              | M1      | Inculcate creative thinking and zeal for research to excel in teaching-learning process                                                                                                               |  |  |  |

|                              | M2      | Create and disseminate technical knowledge in collaboration with industries                                                                                                                           |  |  |  |

| Mission of the Department    | М3      | Provide ethical and value based education by promoting activities for the betterment of the society                                                                                                   |  |  |  |

|                              | M4      | Encourage higher studies, employability skills, entrepreneurship and research to produce efficient professionals thereby adding value to the nation's economy                                         |  |  |  |

|                          | PO 1  | Engineering knowledge: Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.                                                                                                                  |

|--------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | PO 2  | Problem analysis: Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.                                                                 |

|                          | PO 3  | Design/development of solutions: Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations          |

|                          | PO 4  | Conduct investigations of complex problems: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.                                                                |

|                          | PO 5  | Modern tool usage: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.                                                                 |

| PROGRAM<br>OUTCOMES (PO) | PO 6  | The engineer and society: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.                                                               |

|                          | PO 7  | Environment and sustainability: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.                                                                                   |

|                          | PO 8  | Ethics: Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.                                                                                                                                                                    |

|                          | PO 9  | Individual and team work: Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.                                                                                                                                                   |

|                          | PO 10 | Communication: Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions. |

|                          | PO 11 | Project management and finance: Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.                                               |

|                          | PO 12 | Life-long learning: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.                                                                                                                 |

|                                     | I          |                                                                                                                                                                                                           |

|-------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | PEO<br>I   | Produce technically competent graduates with a solid foundation in the field of Electronics and Communication Engineering with the ability to analyze, design, develop, and implement electronic systems. |

| PROGRAM<br>EDUCATIONAL              | PEO<br>II  | Motivate the students for choosing the successful career choices in both public and private sectors by imparting professional development activities.                                                     |

| OBJECTIVES (PEOS)                   | PEO<br>III | Inculcate the ethical values, effective communication skills and develop the ability to integrate engineering skills to broader social needs to the students.                                             |

|                                     | PEO<br>IV  | Impart professional competence, desire for lifelong learning and leadership skills in the field of Electronics and Communication Engineering.                                                             |

|                                     | PSO<br>1   | Design, develop and analyze electronic systems through application of relevant electronics, mathematics and engineering principles.                                                                       |

| PROGRAM SPECIFIC<br>OUTCOMES (PSOs) | PSO 2      | Design, develop and analyze communication systems through application of fundamentals from communication principles, signal processing, and RF System Design & Electromagnetics.                          |

|                                     | PSO<br>3   | Adapt to emerging electronics and communication technologies and develop innovative solutions for existing and newer problems.                                                                            |

#### **INSTRUCTIONS**

#### The students are requested to

- Use this lab manual as observation notebook.

- Bring the lab manual compulsorily for all lab classes.

- Get the verified signature from the staff in charge, once the experiment is completed and output seal should be endorsed and get the staff signature on that lab class itself.

- Get the record correction for the experiment, before entering the next lab class otherwise entry will be denied.

- "Get completed signature in the index page of the record from the staff-in charge" after the completion of all experiments

- Before entering the university practical examinations, the students must get the bonafide signature in the observation and record notebook.

#### **INDEX**

| S.No. | Date | Name of the Experiment | Page<br>No. | Date of submission | Marks | Sign. |

|-------|------|------------------------|-------------|--------------------|-------|-------|

|       |      |                        |             |                    |       |       |

|       |      |                        |             |                    |       |       |

|       |      |                        |             |                    |       |       |

|       |      |                        |             |                    |       |       |

|       |      |                        |             |                    |       |       |

|       |      |                        |             |                    |       |       |

|       |      |                        |             |                    |       |       |

|       |      |                        |             |                    |       |       |

|       |      |                        |             |                    |       |       |

|       |      |                        |             |                    |       |       |

|       |      |                        |             |                    |       |       |

|       |      |                        |             |                    |       |       |

|       |      |                        |             |                    |       |       |

| C N  | Data | N 641 F                | Page | Date of    | N/L - I - | C'-   |

|------|------|------------------------|------|------------|-----------|-------|

| S.No | Date | Name of the Experiment | No.  | submission | Marks     | Sign. |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

|      |      |                        |      |            |           |       |

#### JEPPIAAR ENGINEERING COLLEGE

# DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS ENGINEERING EC 3462- LINEAR INTEGRATED CIRCUITS LAB

#### **SYLLABUS**

#### **LIST OF EXPERIMENTS:**

#### DESIGN AND ANALYSIS OF THE FOLLOWING CIRCUITS

- 1. Series and Shunt feedback amplifiers-Frequency response, Input and output impedance

- 2. RC Phase shift oscillator and Wien Bridge Oscillator

- 3. Hartley Oscillator and Colpitts Oscillator

- 4. RC Integrator and Differentiator circuits using Op-Amp

- 5. Clippers and Clampers

- 6. Instrumentation amplifier

- 7. Active low-pass, High pass & Band pass filters

- 8. PLL Characteristics and its use as frequency multiplier, clock synchronization

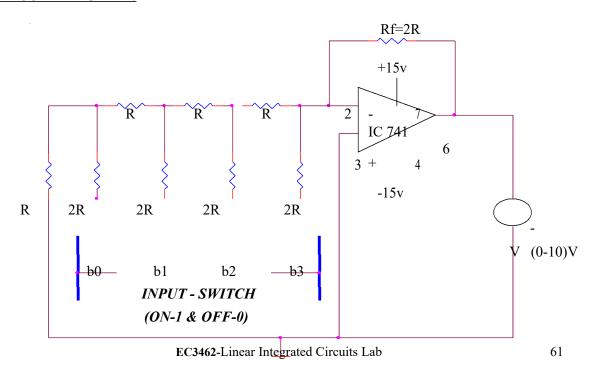

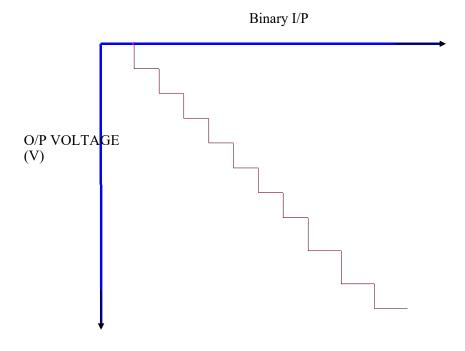

- 9. R-2R ladder type D-A converter using Op-Amp

#### **SIMULATION USING SPICE (Using Transistor):**

- 1. Tuned Collector Oscillator

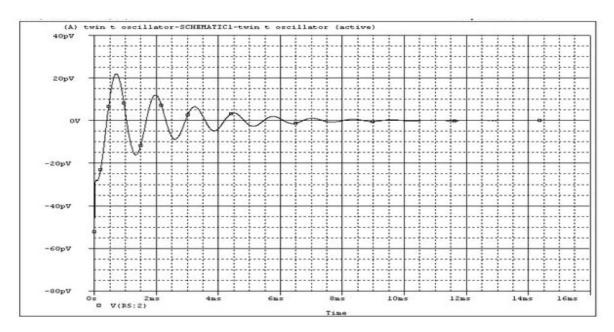

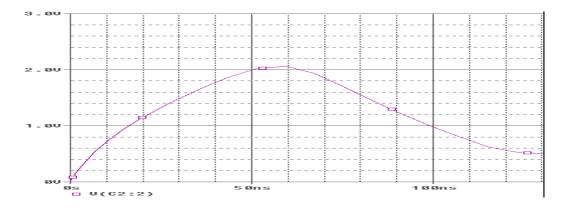

- 2. Twin -T Oscillator / Wein Bridge Oscillator

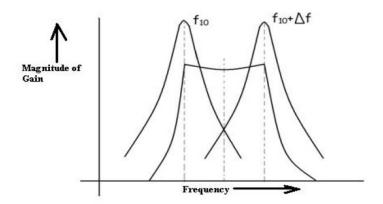

- 3. Double and Stagger tuned Amplifiers

- 4. Bistable Multivibrator

- 5. Schmitt Trigger circuit with Predictable hysteresis

- 6. Analysis of power amplifier

#### **COURSE OBJECTIVES:**

- To gain hands on experience in designing electronic circuits

- To learn simulation software used in circuit design 85

- To learn the fundamental principles of amplifier circuits

- To differentiate feedback amplifiers and oscillators.

- To differentiate the operation of various multivibrators

#### **COURSE OUTCOMES:**

At the end of the course the students will be able to

- Analyze various types of feedback amplifiers

- Design oscillators, tuned amplifiers, wave-shaping circuits and multivibrators

- Design and simulate feedback amplifiers, oscillators, tuned amplifiers, waveshaping circuits and multivibrators, filters using SPICE Tool.

- Design amplifiers, oscillators, D-A converters using operational amplifiers.

- Design filters using op-amp and perform an experiment on frequency response

#### LIST OF EXPERIMENS:

#### **CYCLE I:**

- 1. Series and Shunt feedback amplifiers

- 2. RC Phase shift oscillator

- 3. Wien Bridge Oscillator

- 4. Hartley Oscillator

- 5. Colpitts Oscillator

#### **CYCLE II:**

- 6. RC Integrator and Differentiator circuits using Op-Amp

- 7. Clippers and Clampers

- 8. Instrumentation amplifier

- 9. Active low-pass using Op-Amp

- 10. Active High pass using Op-Amp

- 11. Active Band pass filters using Op-Amp

- 12. PLL Characteristics and its use as frequency multiplier, clock synchronization

- 13. R-2R ladder type D-A converter using Op-Amp

#### CYCLE III: SIMULATION USING SPICE (Using Transistor):

- 14. Tuned Collector Oscillator

- 15. Twin -T Oscillator / Wein Bridge Oscillator

- 16. Double and Stagger tuned Amplifiers

- 17. Bistable Multivibrator

- 18. Schmitt Trigger circuit with Predictable hysteresis

- 19. Analysis of power amplifier

| Ex. No: |                                     |

|---------|-------------------------------------|

|         | SERIES AND SHUNT FEEDBACK AMPLIFIER |

| DATE:   | SERIES AND SHOWI FEEDBACK AND ENTER |

#### AIM:

To design and test the current series and voltage shunt Feedback Amplifier and to compare its frequency response with and without feedback.

#### **APPARATUS REQUIRED:**

| S.NO | COMPONENTS         | RANGE                                     | QTY |

|------|--------------------|-------------------------------------------|-----|

| 1    | Transistor         | BC107                                     |     |

| 2    |                    | $10k\Omega$ , $47k\Omega$ ,               | 2   |

|      | Resistors          | $60k\Omega$ , $1.2k\Omega$ , $1k\Omega$ , | 1   |

|      |                    | 4.7kΩ                                     | 2   |

| 3    | Capacitor          | 10μf,5μf, 47μf,                           | 2   |

| 4    | CRO                | (0-30 )MHz                                | 1   |

| 5    | RPS                | (0-30)V                                   | 1   |

| 6    | Function generator | -                                         | 1   |

| 7    | Breadboard         | -                                         | 1   |

| 8    | Connecting wires   |                                           | -   |

#### **THEORY:**

An amplifier whose function fraction of output is fed back to the input is called feedback amplifier. Depending upon whether the input is in phase or out of phase with the feedback signal, they are classified in to positive feedback and negative feedback. If the feedback signal is in phase with the input, then the wave will have positive gain. Then the amplifier is said to have a positive feedback. If the feedback signal is out of phase with the input, then the wave will have a negative gain. The amplifier is said to have a negative feedback. The values of voltage gain and bandwidth without feedback.

#### **PROCEDURE:**

The connections are made as shown in the circuit. The amplifier is checked for its correct operation .Set the input voltage to a fixed value. Keeping the input voltage Vary the input frequency from 0Hz to 1MHz and note down the corresponding output voltage. plot the graph: gain (dB) vs frequency .Find the input and output impedances. Calculate the bandwidth from the graph. Remove RE and follow the same procedure.

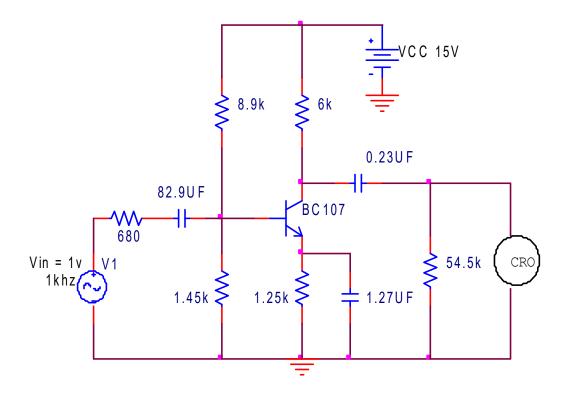

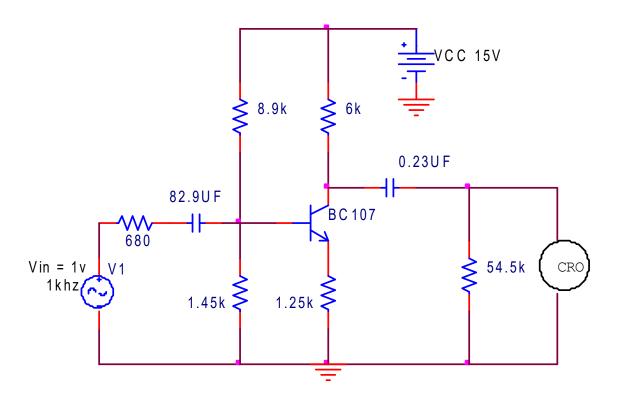

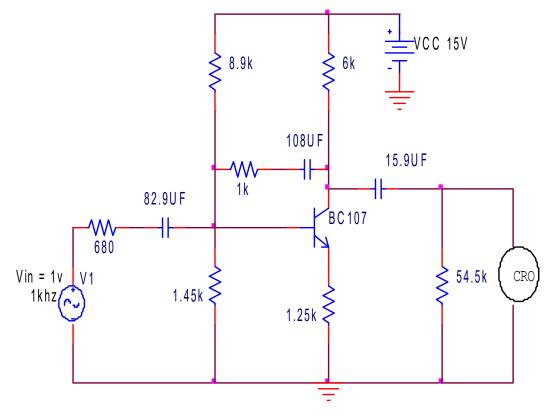

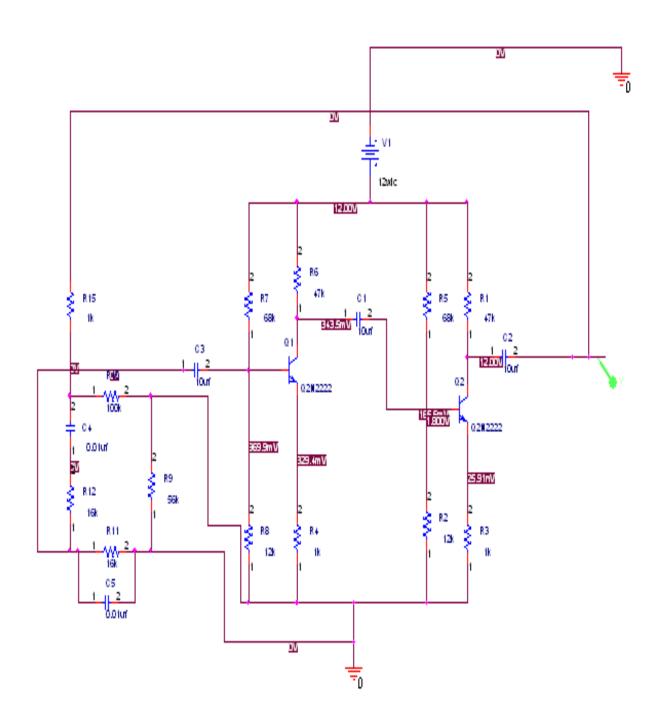

## CURRENT SERIES: CIRCUIT DIAGRAM:

| With Oi | With Out Feedback |           |                   | Volts                   |

|---------|-------------------|-----------|-------------------|-------------------------|

|         | S.No              | Frequency | O/P voltage<br>Vo | Gain<br>Av=20 log Vo/Vi |

|         |                   |           |                   |                         |

|         |                   |           |                   |                         |

|         |                   |           |                   |                         |

|         |                   |           |                   |                         |

|         |                   |           |                   |                         |

|         |                   |           |                   |                         |

|         |                   |           |                   |                         |

|         |                   |           |                   |                         |

|         |                   |           |                   |                         |

|         |                   |           |                   |                         |

| With F  | eedback           |           | Vin =             | Volts                   |

| S.No | Frequency | O/P voltage<br>Vo | Gain<br>Av=20 log Vo/Vi |

|------|-----------|-------------------|-------------------------|

|      |           |                   |                         |

|      |           |                   |                         |

|      |           |                   |                         |

|      |           |                   |                         |

|      |           |                   |                         |

|      |           |                   |                         |

|      |           |                   |                         |

DESIGN SPECIFICATION:

Vcc=12v Ic =1mA  $Av_F = 100$   $Vc_E = 6v$  f=50H<sub>z</sub>

#### Selection of RE & RC:

$$\begin{split} V_{CC} &= I_C(R_C + R_E) \, + \, V_{CE} \\ R_C \, + \, R_E &= \underbrace{V_{CC} - \, V_{CE}}_{I_C} \\ &= \underbrace{12 - 5}_{2 \times 10^{-3}} = 3.5 K\Omega \\ A_{VF} &= -R_C \, / \, R_E \\ &\therefore \, R_C \, = -A_{VF} \, R_E \\ &= -5 R_E \\ -5 R_E \, + \, R_E \, = 3.5 K\Omega \\ &\therefore \, R_E \, = 875 \Omega \\ \text{Choose } R_E \, = 1 K\Omega \\ R_C &= -5 \times 1 \times 10^3 = 5 K\Omega \end{split} \qquad \begin{aligned} \text{Choose } &C_C \, = \, 10 \mu F \end{aligned}$$

#### Selection of R<sub>1</sub>&R<sub>2</sub>:

Choose  $R_c = 4.7K\Omega$

$$V_{R2} = V_{BE} + V_{RE} = V_{BE} + I_C R_E$$

=

$$0.6 + 2 \times 10^{-3} \times 1 \times 10^{3}$$

=  $2.6$ V

$$V_{R1} = V_{CC} - V_{R2}$$

$$= 12 - 2.6 = 9.4V$$

$$\frac{v_{R1}}{v_{R2}} = R^1/_{R2} = 9.4/_{2.6} = 3.615$$

Choose

$$R_2 = 10K\Omega$$

$$R_1 = 3.615 \times 10 \times 10^3$$

=36.15K $\Omega$

Choose

$$R_1 = 47K\Omega$$

#### Selection of Cc & CE

$$X_{CC} \le 0.1R_E$$

$$C_E \ge \frac{1}{2\pi F R_E \times 0.1}$$

$$C_E \ge \frac{1}{2\pi \times 50 \times 1 \times 10^3 \times 0.1}$$

$$C_E \ge 31.83 \mu F$$

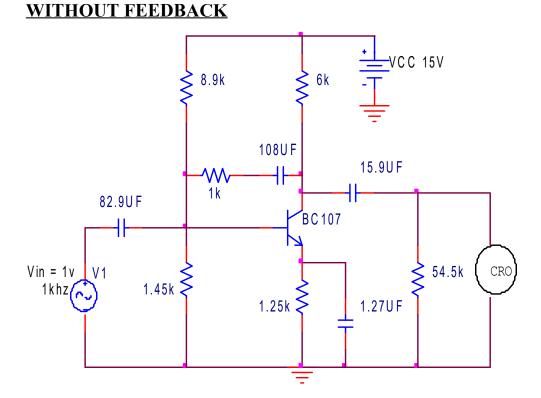

#### **VOLTAGE SHUNT:**

### **CIRCUIT DIAGRAM:**

#### **WITH FEEDBACK**

#### **Observation:**

## CURRENT SERIES: With Out Feedback

With Feedback

| out Feedback |      |           | Vin =             | Volts                   |

|--------------|------|-----------|-------------------|-------------------------|

|              | S.No | Frequency | O/P voltage<br>Vo | Gain<br>Av=20 log Vo/Vi |

|              |      |           |                   |                         |

|              |      |           |                   |                         |

|              |      |           |                   |                         |

|              |      |           |                   |                         |

|              |      |           |                   |                         |

|              |      |           |                   |                         |

|              |      |           |                   |                         |

|              |      |           |                   |                         |

|              |      |           |                   |                         |

|              |      |           |                   |                         |

|              |      |           |                   |                         |

Vin = ----- Volts

S.No Frequency O/P voltage Vo Av=20 log Vo/Vi

#### **DESIGN CALCULATION:**

#### Design specification:

#### Vcc=12v Ic =1 mA $Av_E$ =100 $Vc_E$ = 6v

#### Selection of RE:

$$\begin{split} V_{RE} = & \underbrace{0.1, V_{CC}}_{\text{RE}} = 0.1 \times 12 = 1.2 \text{v} \\ V_{RE} = & \text{Ic R}_{\text{E}} \\ R_{\text{E}} = & \underbrace{\frac{V_{RE}}{\text{Ic}}}_{\text{RE}} = \frac{1.2}{1 \times 10^{-3}} \\ R_{\text{E}} = & 1.2 \text{k}\Omega \end{split}$$

#### Selection of Rc:

$$Vcc = I_ER_E + Vc_E + Ic Rc$$

#### Selection of R1&R2:

$$V_{R2} = V_{BE} + V_{RE}$$

$= 0.6 + 1.2 = 1.8 \text{ V}$

$V_{R1} = V_{GC} - V_{R1}$

$= 12 - 1.8 = 10.2 \text{ V}$

$\frac{V_{R1}}{V_{R2}} = \frac{R^{1}}{R^{2}} = \frac{10.2}{1.8}$

$= 5.67$

Choose  $R_{2} = 10 \text{ K}\Omega$

$R_{1} = 5.6 \times 10 \times 10^{3}$

$= 56.7 \text{ K}\Omega$

Choose  $R_{1} = 47 \text{ K}\Omega$

#### Selection of RF:

$$A_{VF} = -R_F / R_S$$

$-R_F = -A_{VF} R_S$

Choose  $R_S = 600\Omega$

$-R_F = -100 \times 600 = 60K\Omega$

Choose  $R_F = 60K\Omega$

#### Selection of CE:

$$\begin{split} &\mathcal{X}_{CE} \leq 0.1 R_E \\ &\frac{1}{2\pi F \ \mathcal{C}_E} \leq 0.1 \ R_E \ -> \ \ \mathcal{C}_E \geq \frac{1}{2\pi F \ R_E \times 0.1} \\ &\mathcal{C}_E \geq \frac{1}{2\pi \times 50 \times 1.2 \times 10^3 \times 0.1} \end{split}$$

$$C_E \geq 26.52 \mu F$$

Choose

$$C_E = 47 \mu F$$

#### Selection of Cc:

$$\begin{split} &X_{CC} \leq 0.1R_C \\ &\frac{1}{2\pi F \ C_C} \leq 0.1 \ R_C \\ &C_C \geq \frac{1}{2\pi F \ R_C \times 0.1} \\ &C_C \geq \frac{1}{2\pi \times 50 \times 4.7 \times 10^3 \times 0.1} \end{split}$$

$$C_C \geq 6.77 \mu F$$

Choose

$$C_c = 5\mu F$$

#### **RESULT:**

Thus the current series and voltage shunt feedback amplifier is constructed and frequency response is plotted.

| VALUES           |  | CURRENT SERIES | VOLTAGE SHUNT |  |

|------------------|--|----------------|---------------|--|

| Without Feedback |  |                |               |  |

| With Feedback    |  |                |               |  |

| EX. NO:          |  |                |               |  |

| DATE: | RC PHASE SHIFT OSCILLATOR |

|-------|---------------------------|

|       |                           |

#### AIM:

To design and construct the transistor Phase shift oscillator.

#### **APPARATUS REQUIRED:**

| S.NO | COMPONENTS       | RANGE                                                  | QTY   |

|------|------------------|--------------------------------------------------------|-------|

| 1    | Transistor       | BC107                                                  | 1     |

| 2    | Resistor         | $2k\Omega$ , $1k\Omega$ , $25.17k\Omega$ , $10k\Omega$ | 1each |

|      |                  | 4.7ΚΩ                                                  | 3     |

| 3    | Capacitor        |                                                        | 1     |

|      |                  | 5μf, 100 μf0.02μf                                      |       |

|      |                  |                                                        | 3     |

| 4    | CRO              | (0-30)MHz                                              | 1     |

| 5    | RPS              | (0-30) V                                               | 1     |

| 6    | Connecting wires | -                                                      | -     |

| 7    | Breadboard       | -                                                      | 1     |

#### THEORY:

The Transistor Phase Shift Oscillator produces a sine wave of desired designed frequency. The RC combination will give a 60 phase shift totally three combination will give a 180 phase shift. The BC107 is in the common emitter configuration. Therefore that will give a 180 phase shift totally a 360 phase shift output is produced. The capacitor value is designed in order to get the desired output frequency. Initially the C and R are connected as a feedback with respect to input and output and this will maintain constant sine wave output. CRO is connected at the output

#### **PROCEDURE:**

- 1. The circuit is constructed as per the given circuit diagram.

- 2. 7Switch on the power supply and observe the output on the CRO( sine wave)

- 3. Note down the practical frequency and compare it with the theoretical frequency.

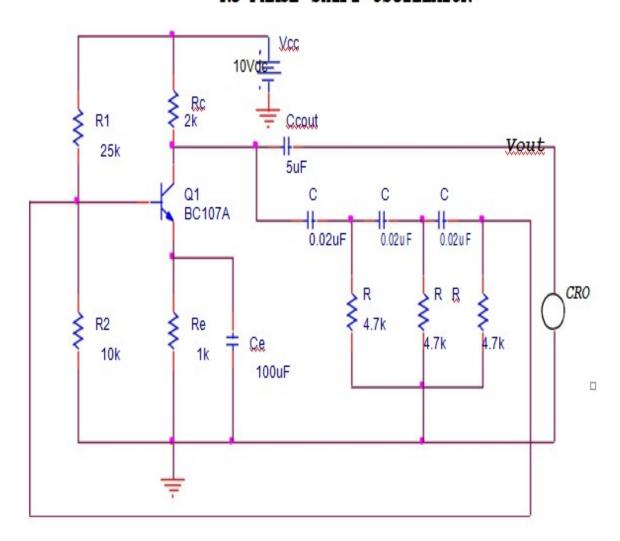

#### **CIRCUIT DIAGRAM:**

#### RC PHASE SHIFT OSCILLATOR

#### **OBSERVATION:PRACTICAL:-**

| Amplitude (V) | Time period(ms) | Frequency(H <sub>Z</sub> ) |

|---------------|-----------------|----------------------------|

|               |                 |                            |

|               |                 |                            |

|               |                 |                            |

#### THEORETICAL:-

Frequency =  $1/2\pi RC\sqrt{6} = 1 \text{ KHZ}$

#### **DESIGN SPECIFICATION:**

$$Vcc=10v$$

Ic =2mA

$H_{fe}=2000$  Ay = 100

#### Selection of RC:

$$\begin{array}{ll} Av_F = 100 & Vc_E = 4 \\ V_{BE} = 0.7V \end{array}$$

$$= \frac{H_{fe} R_C}{H_{ie}}$$

$$R_c = A_V H_{ie} =$$

$$\begin{array}{r}

100 \times 2000 \\

\hline

100 \\

=2k\Omega

\end{array}$$

#### Selection of RE

$$Vec = I_E R_E + Ve_E + I_C R_C R_E = V_{CC} I_C R_C - V_{CE}$$

$$= \underbrace{10 - 4 \cdot 2 \times 10^{-3} \times 2 \times 10^3}_{2 \times 10^{-3}}$$

$$R_E = 1k\Omega$$

$$= R_E - 1K\Omega$$

#### Selection of R1&R2:

$$V_{R2} = V_{BE} + V_{RE} = V_{BE} + I_C R_E$$

= 0.7 + 2 × 10<sup>-3</sup> × 1 × 10<sup>3</sup>

=2.7V

$V_{R1} = V_{GC} - V_{R2}$

= 10 - 2.7 = 7.3V

$\frac{V_{R1}}{V_{R2}} = \frac{R^1}{R^2} = \frac{7.3}{2.7} = 2.7037$

Choose  $R_2 = 10K\Omega$

$R_1 = 2.7037 \times 10 \times 10^3$

=27K $\Omega$

Choose  $R_1 = 25K\Omega$

#### Selection of $C_E$ :

$$\begin{split} &X_{CE} \leq 0.1R_{E} \\ &\frac{1}{2\pi F \; C_{E}} \leq 0.1 \; R_{E} \; -> \; C_{E} \geq \frac{1}{2\pi F \; R_{E} \times 0.1} \\ &C_{E} \; \geq \frac{1}{2\pi \times 50 \times 1000 \times 0.1} \\ &C_{E} \; \geq 31.8 \mu F \\ &\text{Choose} \; C_{E} = \; 100 \mu F \end{split}$$

#### **RESULT:**

Thus the RC Phase Shift Oscillator is designed and the output is verified Theoretical frequency =

Practical frequency =

## EX. NO:

#### Selection of Cc:

$$\begin{split} X_{CC} &\leq 0.1 R_C \\ \frac{1}{2\pi F \ C_C} &\leq 0.1 \ R_C \\ C_C &\geq \frac{1}{2\pi F \ R_C \times 0.1} \\ C_C &\geq \frac{1}{2\pi \times 50 \times 2000 \times 0.1} \end{split}$$

$$C_C \ge 15.9 \mu F$$

Choose  $C_C = 5 \mu F$

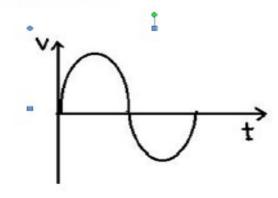

#### MODEL GRAPH:

|       | Wien – Bridge Oscillator               |

|-------|----------------------------------------|

| DATE: | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

|       |                                        |

#### AIM:

To Design and construct a Wien – Bridge Oscillator for a given cut-off frequency. **APPARATUS REQUIRED:**

| S.NO | COMPONENTS       | RANGE                                      | QTY   |

|------|------------------|--------------------------------------------|-------|

| 1    | Transistor       | BC 107                                     | 1     |

| 2    | Resistor         | 10kΩ, $2.7$ kΩ, $47$ kΩ, $4.7$ kΩ, $680$ Ω | 2each |

| 3    | Capacitor        | 47 μf, 0.01 μf,                            | 1,2   |

| 4    | CRO              | (0-30 )MHz                                 | 1     |

| 5    | RPS              | (0-30) V                                   | 1     |

| 6    | Breadboard       | -                                          | 1     |

| 7    | Connecting wires | -                                          | -     |

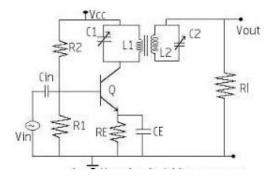

#### **CIRCUIT DIAGRAM**:

#### DESIGN SPECIFICATION:

$$Vcc=12v$$

$Ic=2mA$

$Av_E=100$

$Vc_E=50\%$  of  $V_{CC}=6V$

$V_{RE}=10\%$  of  $V_{CC}=1.2V$

$V_{RC}=40\%$  of  $V_{CC}=4.8V$

$h_{fe}=100$

$F=1KH_Z$

#### Selection of R<sub>C</sub>

$$V_{RC} = \underbrace{\frac{I_C}{V_{RC}}}_{R_C} = \underbrace{\frac{4.8}{2 \times 10^{-3}}}_{R_C = 2.4k\Omega}$$

#### Selection of RE:

$$V_{RE} = IE RE$$

$$V_{RE} = \frac{V_{RE}}{Ic} = \frac{1.2}{2 \times 10^{-3}}$$

$$R_{E} = 600\Omega$$

$$Choose R_{E} = 680\Omega$$

#### Selection of R1&R2:

$$V_{R2} = V_{BE} + V_{RE}$$

= 0.7 + 1.2

=1.9V

$V_{R1} = V_{CC} - V_{R2}$

= 12 - 1.9 = 10.1V

$\frac{V_{R1}}{V_{R2}} = \frac{R1}{R2} = \frac{10.1}{1.9} = 5.315$

Choose  $R_2 = 10K\Omega$

$R_1 = 5.315 \times 10 \times 10^3$

= 47K $\Omega$

Choose  $R_1 = 47K\Omega$

#### Selection of CC:

$$\frac{1}{2\pi C_{C}(R_{1}||R_{2}||hR)_{e}} = C_{C} \ge \frac{1}{2\pi \times 1000 \times [47k||10k||68k]}$$

$$C_C \ge 21.958 \mu F$$

#### THEORY:

In Wien bridge oscillator, Wien bridge circuit is connected between the amplifier input terminals and output terminals. The bridge has a series RC network in one arm and parallel network in the adjoining arm. In the remaining 2 arms of the bridge resistors R1and Rf are connected. To maintain oscillations total phase shift around the circuit must be zero and loop

gain unity. First condition occurs only when the bridge is balanced. Assuming that the resistors and capacitors are equal in value, the resonant frequency of balanced bridge is given by

$$Fo = 0.159 RC$$

#### **PROCEDURE:**

- 1. The circuit is constructed as per the given circuit diagram.

- 2. Switch on the power supply and observe the output on the CRO

- 3. (sine wave)

- 4. Note down the practical frequency and compare it with the theoretical frequency.

#### **MODEL GRAPH:**

#### **OBSERVATION:**

| AMPLITUDE (V) | TIME (ms) | FREQUENCY(H <sub>Z</sub> ) |

|---------------|-----------|----------------------------|

|               |           |                            |

|               |           |                            |

|               |           |                            |

|               |           |                            |

#### **RESULT:**

Thus the Wien bridge oscillator is designed and the output is drawn.

#### AIM:

To Design and construct the given Oscillator at the given operating frequency.

#### **APPARATUS REQUIRED:**

| S.NO | COMPONENTS         | RANGE                     | QTY      |

|------|--------------------|---------------------------|----------|

| 1    | Transistor         | BC 107                    | 1        |

| 2    | Resistor           | $8.5k\Omega,3.3k\Omega,$  | Each one |

|      |                    | $600\Omega$ , $47k\Omega$ |          |

| 3    | Capacitor          | 4.7µf, 0.1 µf             | Each one |

|      |                    |                           |          |

| 4    | Inductor           | 20mH                      | 2        |

| 5    | CRO                | (0-30)MHz                 | 1        |

| 6    | RPS                | (0-30) V                  | 1        |

| 7    | Function Generator | (0-1)MHZ                  | 1        |

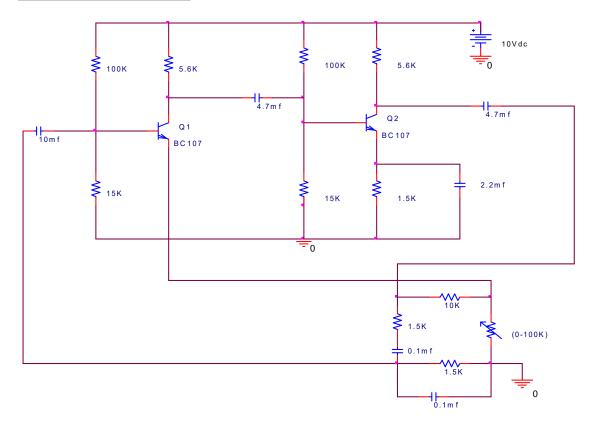

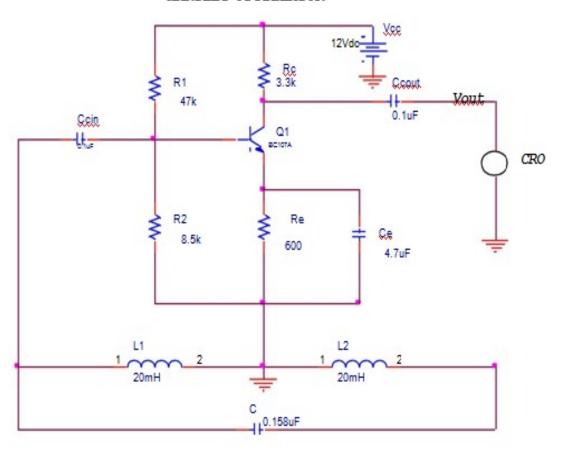

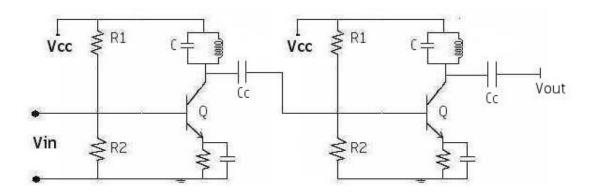

#### CIRCUIT DIAGRAM:

#### HARTLEY OSCILLATOR

#### DESIGN SPECIFICATION.

Vcc=12v Ic =2mA VcF =5V S=12

$$5v$$

h<sub>ft</sub> = 125  $F = 2KH_Z$

Selection of  $R_C \& R_E$ :

$$V_{CC} = I_{C}(R_{C} + R_{E}) + V_{CE}$$

$R_{C} + R_{E} = V_{CC} - V_{CE}$

$I_{C}$

$V_{RE} = 0.1V_{CC} = 0.1 \times 12 = 1.2V$

$V_{RE} = I_{E}R_{E}$

$R_{E} = V_{RE}$

$I_{C}$

$= \frac{1.2}{2 \times 10^{-3}} = 600\Omega$

$R_{C} = (R_{C} + R_{E}) - R_{E}$

#### Selection of R1&R2:

$$S = \frac{1+\beta}{1+\beta \left(\frac{Re}{Re+Rb}\right)}$$

$$12 = \frac{1+125}{1+125\left(\frac{600}{600+Rb}\right)}$$

$$R_B = 7.29 \text{K}\Omega$$

$V_{R2} = V_{BE} + I_E R_E$

$= 0.6 \times 2 \times 10_{-3} \times 600$

$= 1.8 \text{V}$

$$R_{2} = \frac{Vcc}{R1 + R2} R2 \Longrightarrow \frac{VR2}{Vcc} = \frac{R2}{R1 + R2}$$

$$\frac{R2}{R1 + R2} = \frac{VR2}{Vcc} = \frac{1}{12} 8 = 0.15$$

$$R_B = \frac{R_1R_2}{R_1 + R_2} = 7.29 \text{K}\Omega$$

$$0.15R_1 = 7.29K\Omega$$

$$R_1 = 48.6 \frac{K\Omega \text{Choose}}{K\Omega \text{Choose}} R_1 = 47 K\Omega$$

$$\begin{array}{ll} \frac{R2}{R1+R2} & = 0.15 \\ R_2 = 0. \ \underline{15} \ R_2 + 0. \ \underline{15} \ R_1 \\ 0.85 \ R_2 = 0. \ \underline{15} \ R_1 \\ R_2 = 0.176 & \times 47 \times 10^{-3} \\ R_2 = 8.5 \mathrm{K}\Omega \end{array}$$

#### Selection of $C_E$ :

$$\begin{split} &X_{CE} \leq 0.1R_E \\ &\frac{1}{2\pi F \; C_E} \leq 0.1 \; R_E \quad \ \ -> \; C_E \, \geq \, \frac{1}{2\pi F \; R_E \times 0.1} \end{split}$$

# $\frac{\text{Selection of } C_C:}{X_{CC} \leq 0.1R_C}$ $\frac{1}{2\pi F C_C} \leq 0.1 R_C$ $C_C \geq \frac{1}{2\pi F R_C \times 0.1}$

## Selection of L1L2 &C:

$$F = \frac{1}{2\pi\sqrt{Leq C}}$$

$$Leq = L_1 L_2$$

$$L_1 = L_2 = 20mH$$

$$Leq = 40mH$$

$$C = \frac{1}{4\pi^2 f^2 Leq}$$

$$= \frac{1}{4\pi^2 \times 4 \times 10^6 \times 40 \times 10^{-3}}$$

$$0.158 \, \mu f \, Choose$$

$$C = 0.1 \, \mu f$$

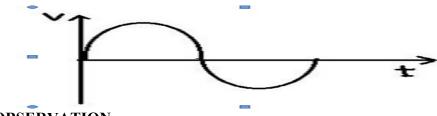

MODELGRAPH:

**THEORY:**

LC oscillator consisting of a tank circuit for generating sine wave of required frequency. Rectifying Barkhausen criteria A for a circuit containing reactance A must be positive and greater than or equal to unity.

**PROCEDURE:**

- 1. The circuit is constructed as per the given circuit diagram.

- 2. Switch on the power supply and observe the output on the CRO ( sine wave)

- 3. Note down the practical frequency and compare it with the theoretical frequency.

**TABULATION:**

| AMPLITUDE (V) | TIME (ms) | FREQUENCY(H <sub>Z</sub> ) |

|---------------|-----------|----------------------------|

|               |           |                            |

|               |           |                            |

|               |           |                            |

|               |           |                            |

**RESULT:**

Thus the Hartley oscillator is designed frequency and the output waveform is drawn.

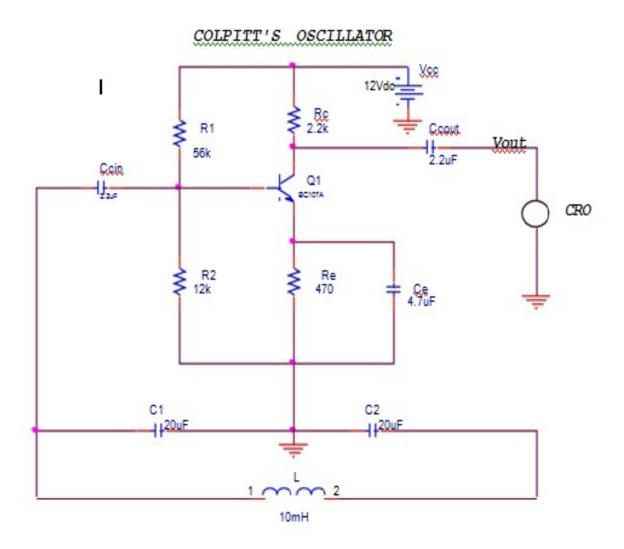

| Ex. No :<br>Date: | COLPITTS OSCILLATOR |

|-------------------|---------------------|

|                   |                     |

#### AIM:

To Design and construct the given Oscillator at the given operating frequency. **APPARATUS REQUIRED:**

| S.NO | COMPONENTS         | RANGE                      | QTY   |

|------|--------------------|----------------------------|-------|

| 1    | Transistor         | BC 107                     | 1     |

| 2    | Resistor           | 56kΩ, $2.2$ kΩ,            | 1each |

|      |                    | $12k\Omega$ , $470k\Omega$ |       |

| 3    | Capacitor          | 4.7μf, 2.2μf,              | 1     |

|      |                    | 0.01 µf                    | 3     |

| 4    | Inductor           | 10mH                       | 1     |

| 5    | CRO                | (0-30)MHz                  | 1     |

| 6    | RPS                | (0-30) V                   | 1     |

| 7    | Function Generator | (0-1)MHZ                   | 1     |

#### **CIRCUIT DIAGRAM:**

#### DESIGN SPECIFICATION.

$$\underline{\underline{V}}_{CE} = 12v$$

$\underline{\underline{I}}_{C} = 2mA$   $\underline{\underline{V}}_{CE} = 5v$   $S = 20$   $\underline{\underline{V}}_{CE} = 5v$   $S = 20$

#### Selection of RE:

$$V_{RE} = 0.1Vcc =$$

$$0.1 \times 12 = 1.2V$$

$$V_{RE} = I_E R_E$$

$$R_E = \frac{V_{RE}}{I_C}$$

$$= \frac{12}{2 \times 10^{-3}} = 600\Omega$$

$$R_C = (R_C R_E) - R_E$$

$$Choose R_E = 470\Omega Vcc$$

$$= I_E R_E + Vc_E + I_C R_C$$

$$R_C = V_{CC} I_E R_E I_C - V_{CE}$$

#### = <u>12-5-2×10<sup>-3</sup>×470</u> 1×10-3 $=3.03\times10^{3}$

Choose  $Rc = 2.2k\Omega$

#### Selection of R1&R2:

$$S = \frac{1+\beta}{1+\beta \left(\frac{Re}{Re+Rb}\right)}$$

$$12 = \frac{1+125}{1+125\left(\frac{470}{470+Rb}\right)}$$

$$R_B = 10.6 \text{K}\Omega$$

$R_B = \frac{R1R2}{R1+R2} = 10.6 \text{K}\Omega$

#### Choose $R_2 = 12k\Omega$

$$\frac{1200R1}{1200+R1} = 10.6 \times 10^3$$

$$R_1 = 60 \text{ K}\Omega$$

Choose  $R_1 = 56k\Omega$

#### Selection of L&C:

$$F = \frac{1}{2\pi} \sqrt{\frac{1}{L}} \left( \frac{C1+C2}{C1C2} \right)$$

$$F^{2} = \frac{1}{4\pi 2} \times \frac{1}{L} \left( \frac{C1+C2}{C1C2} \right)$$

$$Choose L = 10mH$$

$$\frac{C1+C2}{C1C2} = 4\pi^{2}f^{2}L$$

$$= 4\pi^{2} \times 250000 \times 10 \times 10^{-3}$$

$$= 98696.04$$

$$Assume C_{1} = C_{2} = C$$

$$\frac{2C}{C2} = \frac{2}{C} = 98696.04$$

$$C = 20.26\mu f$$

$$Choose C_{1} = C_{2} = 20 \mu f$$

$$\begin{split} &\frac{\text{Selection of } C_E:}{X_{CE}} \leq 0.1R_E \\ &\frac{1}{2\pi F \ C_E} \leq 0.1 \ R_E \quad \ -> \ \ C_E \geq \frac{1}{2\pi F \ R_E \times 0.1} \end{split}$$

$$\frac{\text{Selection of } C_C:}{X_{CC} \leq 0.1R_C}$$

$$\frac{1}{2\pi F C_C} \leq 0.1 R_C$$

$$C_C \geq \frac{1}{2\pi F R_C \times 0.1}$$

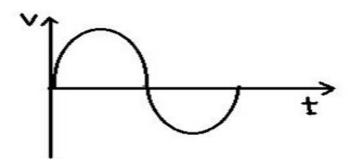

#### MODEL GRAPH:

29

#### THEORY:

LC oscillator consisting of a tank circuit for generating sine wave of required frequency. Rectifying Barkhausen criteria A for a circuit containing reactance A must be positive and greater than or equal to unity.

#### **PROCEDURE:**

- 1. The circuit connection is made as per the circuit diagram.

- 2. Switch on the power supply and observe the output on the CRO(sine wave ).

- 3. Note down the practical frequency and compare it with the theoretical frequency.

#### **TABULATION:**

| AMPLITUDE (V) | TIME (ms) | FREQUENCY(H <sub>Z</sub> ) |

|---------------|-----------|----------------------------|

|               |           |                            |

|               |           |                            |

|               |           |                            |

|               |           |                            |

#### **RESULT:**

Thus the Colpitts oscillator is designed for the given frequency and the output response is verified.

Theoretical value =

Practical value =

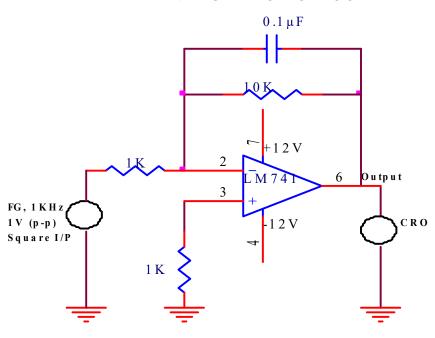

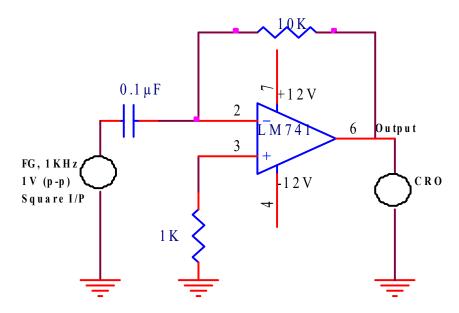

#### **INTEGRATOR AND DIFFERENTIATOR USING OP-AMP.**

Exp. No : Date :

AIM:

To construct the Integrator and Differentiator circuits using Op-amp. IC and study the output waveforms.

#### APPARATUS REQUIRED:

| Sl. No: | Apparatus Name                | Range                  | Qty. |

|---------|-------------------------------|------------------------|------|

| 1       | Operational Amplifier         | IC 741                 | 1    |

| 2       | Resistors                     | 1 ΚΩ                   | 2    |

|         |                               | 10 ΚΩ                  | 1    |

| 3       | Capacitor                     | 0.1μF                  |      |

| 4       | Bread Board                   |                        | 1    |

| 5       | Regulated Power Supply        | <u>+</u> 15V, Dual     | 1    |

| 6       | Function Generator            | (1Hz – 1MHz.)          | 1    |

| 7       | Cathode Ray Oscilloscope      | 20 / 40MHz, Dual Trace | 1    |

| 8       | Connecting Wires & CRO Probes |                        |      |

#### **THEORY:**

Integrator produces a voltage output proportional to the product (multiplication) of the input voltage and time; and the differentiator (not to be confused with differential) produces a voltage output proportional to the input voltage's rate of change.

#### **Differentiator:**

Capacitance can be defined as the measure of a capacitor's opposition to changes in voltage. The greater the capacitance, the more the opposition. Capacitors oppose voltage change by creating current in the circuit: that is, they either charge or discharge in response to a change in applied voltage. So, the more capacitance a capacitor has, the greater its charge or discharge current will be for any given rate of voltage change across it. The equation for this is quite simple:

$$i = C (dv/dt)$$

The dv/dt fraction is a calculus expression representing the rate of voltage changes over time.

Capacitor current moves through the feedback resistor, producing a drop across it, which is the same as the output voltage. A linear, positive rate of input voltage change will result in a steady negative voltage at the output of the Op-amp. Conversely, a linear, negative rate of input voltage change will

result in a steady positive voltage at the output of the op-amp. The faster the rate of voltage changes at the input (either positive or negative), the greater the voltage at the output.

The formula for determining voltage output for the differentiator is as follows:

**Integrator:**

$$Vout = -RC d/dt (Vin)$$

Here, the op-amp circuit would generate an output voltage proportional to the magnitude and duration that an input voltage signal has deviated from 0 volts. Stated differently, a constant input signal would generate a certain rate of change in the output voltage: differentiation in reverse. To do this, all we have to do is swap the capacitor and resistor in the previous circuit:

A simple low pass RC circuit can also work as an Integrator when time constant is very large. This requires very large values of R and C. The components R and C cannot be made infinitely large because of practical limitations. However in the op-amp integrator by Miller's theorem, the effective input capacitance becomes Cf (1-Av), where Av is the gain of the Op-amp. The Gain (Av) is the infinite for an ideal Op-amp, so the effective time constant of the Op-amp Integrator becomes very large which results perfect integration.

The integrator produces a voltage output proportional to the product (multiplication) of the input voltage and time

However, if we apply a constant, positive voltage to the input, the Op-amp output will fall negative at a linear rate, in an attempt to produce the changing voltage across the capacitor necessary to maintain the current established by the voltage difference across the resistor. Conversely, a constant, negative voltage at the input results in a linear, rising (positive) voltage at the output. The output voltage rate-of-change will be proportional to the value of the input voltage.

The formula for determining voltage output for the integrator is as follows:

$$\frac{dv_{out}}{dt} = -\frac{V_{in}}{RC}$$

$$or$$

$$V_{out} = \int_{0}^{t} -\frac{V_{in}}{RC} dt + c$$

$$Where,$$

$$c = Output voltage at start time (t=0)$$

| <b>DESIGN &amp; CALCULATIONS IF AN</b> | <b>DESIGN</b> | & CALCUL | ATIONS | IF ANY: |

|----------------------------------------|---------------|----------|--------|---------|

|----------------------------------------|---------------|----------|--------|---------|

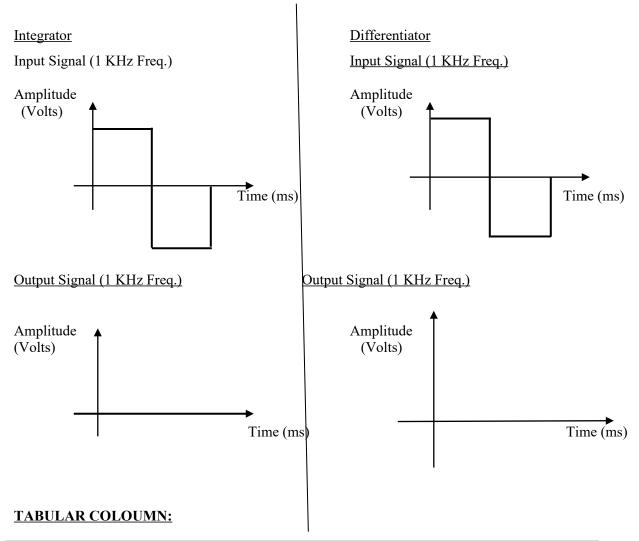

<u>Integrator:</u> <u>Differentiator:</u>

#### **CIRCUIT DIAGRAM:**

#### INTEGRATOR CIRCUIT

#### DIFFERENTIATOR CIRCUIT

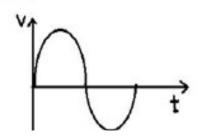

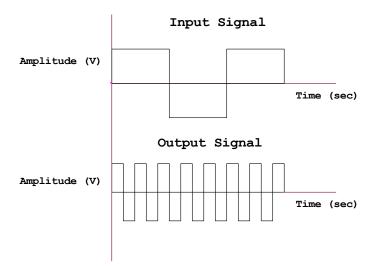

#### **MODEL GRAPH:**

| INTEGRATOR  |              |               | DIFFERENTIATOR |               |

|-------------|--------------|---------------|----------------|---------------|

|             | Input Signal | Output Signal | Input Signal   | Output Signal |

| Amplitude   |              |               |                |               |

| Time Period |              |               |                |               |

| Frequency   |              |               |                |               |

#### **PROCEDURE:**

- 1. Construct the circuit as per Circuit diagram shown in figure.

- 2. Select the Square waveform in Function Generator and set fixed amplitude and fixed frequency say 1V (p-p) and 1 KHz respectively.

- 3. The resistance Rcomp is also connected to the Non-inverting input terminal to minimize the effect of the input bias current.

- 4. Note the corresponding input and output signals (refer model graph) for both Circuits.

- 5. Note the gain of the integrator decreases with increasing frequency.

- 6. Tabulate the noted readings and draw the input and output waveforms in Graph sheet.

#### **RESULT:**

#### **VIVA VOCE:**

1. What are the main drawbacks of ideal differentiator?

At high frequency, differentiators may become unstable and break into oscillation. The input impedance i.e.  $(1/\omega C1)$  decreases with increase in frequency, thereby making the circuit sensitive to high frequency noise.

2. What are the steps to be followed while designing a good differentiator?

Choose fa equal to highest frequency of the input signal. Assume a practical value of C1 ( $<1\mu F$ ) and then calculate Rf.

Choose fb=10fa (Say). Now calculate the values of R1 and C1.

R1C1 = RfCf.

3. What are the main drawbacks of ideal integrator circuit?

At low frequencies such as dc ( $\omega \approx 0$ ) the gain becomes infinite.

When the op-amp saturates i.e. the capacitor is fully charged it behaves like an open circuit.

| EX.NO: |                     |

|--------|---------------------|

| DATE:  | CLIPPER AND CLAMPER |

#### AIM:

To design and study the clipper and clamper circuits.

# **APPARATUS REQUIRED:**

| S.NO | COMPONENTS         | RANGE     | QTY |

|------|--------------------|-----------|-----|

| 1    | Diode              | IN4001    | 1   |

| 2    | Resistor           | 1kΩ       | 1   |

| 3    | CRO                | (0-30)MHz | 1   |

| 4    | RPS                | (0-30) V  | 1   |

| 5    | Function Generator | (0-1)MHZ  | 1   |

| 6    | Breadboard         | -         | 1   |

| 7    | Connecting wires   | -         | 1   |

#### THEORY:

#### **CLIPPERS:**

Clippers have the ability to clip off a portion of the input signal without distorting the remaining part of the alternating waveform. The half wave rectifier is an example of the simplest form of diode clipper – one resistor and diode. Depending upon the orientation of the diode, the positive or negative region of the input signal is clipped off. Clippers are of two: i.Series ii. Parallel. Series configuration is defined as one where diode is in series with the load, while in parallel the diode is connected in parallel to the load.

#### **CLAMPERS:**

The clamping network is one that will clamp a signal to different dc level. The circuit has a diode, resistor and a capacitive element, but it can also employ an independent dc supply to introduce an additional shift. The magnitude of R and C must be chosen that the time constant.  $\tau = RC$  is large enough that the voltage across the capacitor does not discharge significantly during the interval when the diode is non conducting.

#### **PROCEDURE:**

- 1. Connections are given as per the circuit.

- 2. Set input signal voltage (5v,1kHz) using function generator.

- 3. Observe the output waveform using CRO

- 4. Sketch the observed waveform on the graph sheet.

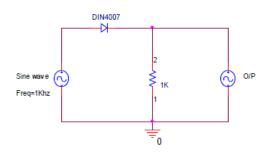

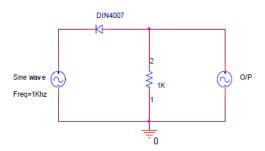

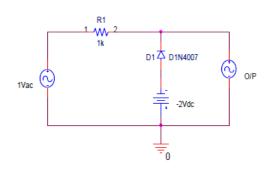

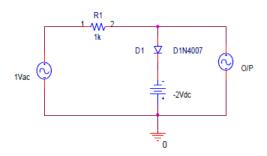

# **CIRCUIT DIAGRAM:**

#### **NEGATIVE CLIPPER:**

#### POSITIVE CLIPPER:

#### POSITIVE BIASED NEGATIVE CLIPPER:

#### POSITIVE BIASED POSITIVE CLIPPER:

#### NEGATIVE BIASED NEGATIVE CLIPPER:

# NEGATIVE BIASED PASITIVE CLIPPER:

# TABULATION:

| WAVE FORM              | AMPLITUDE (V) | TIME PERIOD (ms) |

|------------------------|---------------|------------------|

| INPUT SIGNAL           |               |                  |

| +VE BIASED +VE CLIPPER |               |                  |

| -VE BIASED +VE CLIPPER |  |

|------------------------|--|

| +VE BIASED -VE CLIPPER |  |

| -VE BIASED -VE CLIPPER |  |

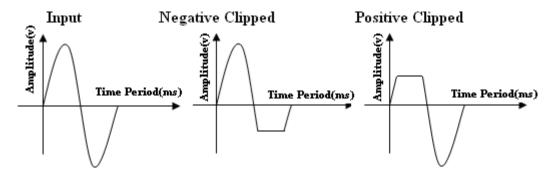

# **MODEL GRAPH:**

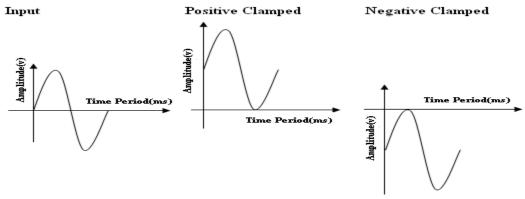

# **CLAMPING CIRCUITS**

AIM: To study the clamping circuits

(a). Positive clamper circuit (b) Negative clamper circuit

# **APPARATUS REQUIRED:**

| S.NO | COMPONENTS         | RANGE     | QTY |

|------|--------------------|-----------|-----|

| 1    | Diode              | IN4001    | 1   |

| 2    | Resistor           | 10kΩ      | 2   |

| 3    | Capacitor          | 0.1 μf    | 1   |

| 4    | CRO                | (0-30)MHz | 1   |

| 5    | RPS                | (0-30) V  | 1   |

| 6    | Function Generator | (0-1)MHZ  | 1   |

| 7    | Breadboard         | -         | 1   |

| 8    | Connecting wires   | -         | -   |

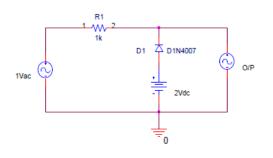

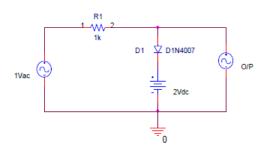

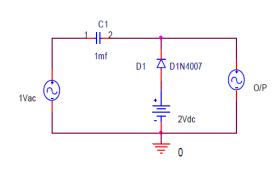

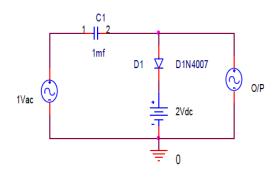

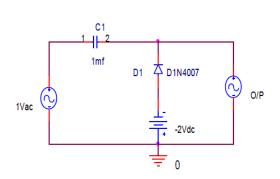

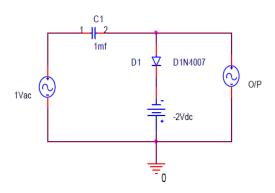

# **CIRCUIT DIAGRAM:**

# POSITIVE CLAMPER:

# NEGATIVE CLAMPER:

#### POSITIVE BIASED POSITIVE CLAMPER:

#### POSITIVE BIASED NEGATIVE CLAMPER:

#### NEGATIVE BIASED POSITIVE CLAMPER:

# NEGATIVE BIASED NEGATIVE CLAMPER:

# TABULATION:

| WAVE FORM      | AMPLITUDE (V) | TIME PERIOD (ms) |

|----------------|---------------|------------------|

| INPUT SIGNAL   |               |                  |

| +VE BIASED +VE |               |                  |

| CLAMPER        |               |                  |

| -VE BIASED +VE |               |                  |

| CLAMPER        |               |                  |

| +VE BIASED -VE |               |                  |

| CLAMPER        |               |                  |

| -VE BIASED -VE |               |                  |

| CLAMPER        |               |                  |

# **MODEL GRAPH:**

# **PROCEDURE:**

- 1. Connections are given as per the circuit.

- 2. Set input signal voltage (5v,1kHz) using function generator.

- 3. Observe the output waveform using CRO.

- 4. Sketch the observed waveform on the graph sheet.

# **RESULT:**

Thus the clipper and clamper circuits are designed and its waveform are observed.

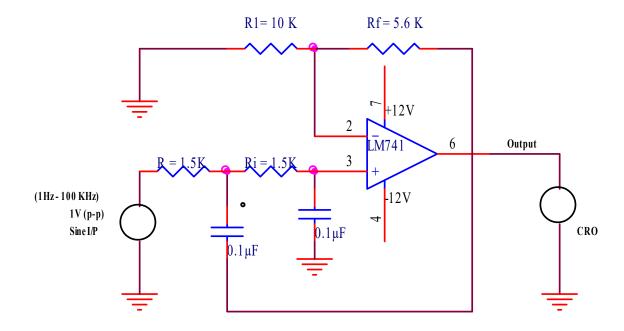

# SECOND ORDER ACTIVE LOW PASS FILTER.

Exp. No :

Date :

#### AIM:

To Design and Construct a second order low pass filter having upper cut off frequency 1 KHz using Op-amp. IC and also determine its frequency response.

# APPARATUS REQUIRED:

| Sl. No: | Apparatus Name                | Range                  | Qty. |

|---------|-------------------------------|------------------------|------|

| 1       | Operational Amplifier         | IC 741                 | 1    |

| 2       | Resistors                     | 10 ΚΩ                  | 1    |

|         |                               | 1.5 ΚΩ                 | 2    |

|         |                               | 5.6 ΚΩ                 | 1    |

| 3       | Capacitor                     | 0.1μF                  | 2    |

| 4       | Bread Board                   |                        | 1    |

| 5       | Regulated Power Supply        | <u>+</u> 15V, Dual     | 1    |

| 6       | Function Generator            | (1Hz – 1MHz.)          | 1    |

| 7       | Cathode Ray Oscilloscope      | 20 / 40MHz, Dual Trace | 1    |

| 8       | Connecting Wires & CRO Probes |                        |      |

# **THEORY:**

An improved filter response can be obtained by using a Second order Active Filter. A second order filter consists of two RC pairs and has a roll-off rate of -40 dB/decade. A general second order filter (Sallen Kay filter) is used to analyze different LP, HP, BP and BSF. A first order filter can be converted to second order type using an additional RC network as shown in circuit diagram. The cut off frequency f<sub>H</sub> for the filter is now decided by R and C. The gain of the filter is usual decided by op-amp i.e. the resistance R3 and Rf.

# **DESIGN & CALCULATIONS IF ANY:**

Given:  $fH = 1 \text{ KHz} = 1/(2\pi RC)$

Let  $C = 0.1 \mu F$ ,  $R = 1.6 K\Omega$

For n = 2,  $\alpha$  (damping factor) = 1.414,

Pass Band Gain =  $Ao = 3 - \alpha = 3 - 1.414 = 1.586$ .

Transfer function of second order Butter worth LPF as:

$$H(s) = \frac{1.586}{S2 + 1.414 s + 1}$$

Now Ao = 1 + (Rf/R1) = 1.586 = 1 + 0.586

Let  $Ri = 10 \text{ K}\Omega$ , then  $Rf = 5.86 \text{ K}\Omega$

# **CIRCUIT DIAGRAM:**

### SECOND ORDER ACTIVE LOW PASS FILTER

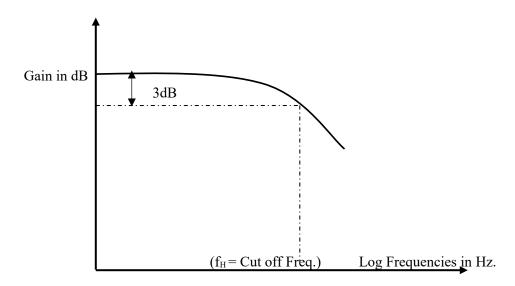

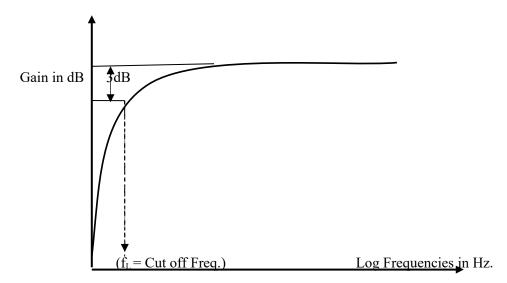

# **MODEL GRAPH:**

# **TABULAR COLOUMN:**

Vin =

| Sl.No. | Frequency (Hz) | Vout (V) | Gain = Vo / Vin | Gain in dB = 20 log Gain |

|--------|----------------|----------|-----------------|--------------------------|

| 1      |                |          |                 |                          |

| 2      |                |          |                 |                          |

| 3      |                |          |                 |                          |

| 4      |                |          |                 |                          |

| 5      |                |          |                 |                          |

| 6      |                |          |                 |                          |

| 7      |                |          |                 |                          |

| 8      |                |          |                 |                          |

| 9      |                |          |                 |                          |

| 10     |                |          |                 |                          |

| 11     |                |          |                 |                          |

| 12     |                |          |                 |                          |

| 13     |                |          |                 |                          |

| 14     |                |          |                 |                          |

| 15     |                |          |                 |                          |

#### **PROCEDURE:**

- 1. Construct the circuit as per Circuit diagram shown in figure.

- 2. Select the Sine waveform in Function Generator and set fixed amplitude and fixed frequency say 1V (p-p) and 1 KHz respectively.

- 3. Observe the output waveform for different frequency ranges (start from 50 Hz to beyond some value of cut of frequency)

- 4. Note the readings observed on CRO and find its gain for different frequency ranges.

- 5. Draw the graph for its Gain in dB Vs. Frequency and find its Cut off frequency.

# **RESULT:**

#### **VIVA VOCE:**

1. What are the main drawbacks of ideal differentiator?

At high frequency, differentiators may become unstable and break into oscillation. The input impedance i.e.  $(1/\omega C1)$  decreases with increase in frequency, thereby making the circuit sensitive to high frequency noise.

2. What are the steps to be followed while designing a good differentiator?

Choose fa equal to highest frequency of the input signal. Assume a practical value of C1 ( $<1\mu F$ ) and then calculate Rf.

Choose fb=10fa (Say). Now calculate the values of R1 and C1.

R1C1 = RfCf.

3. What are the main drawbacks of ideal integrator circuit?

At low frequencies such as dc ( $\omega \approx 0$ ) the gain becomes infinite.

When the op-amp saturates i.e. the capacitor is fully charged it behaves like an open circuit.

#### SECOND ORDER ACTIVE HIGH PASS FILTER.

Exp. No : Date :

AIM:

To Design and Construct a second order low pass filter having upper cut off frequency 1 KHz using Op-amp. IC and also determine its frequency response.

# APPARATUS REQUIRED:

| Sl. No: | Apparatus Name                | Range                  | Qty. |

|---------|-------------------------------|------------------------|------|

| 1       | Operational Amplifier         | IC 741                 | 1    |

| 2       | Resistors                     |                        |      |

| 3       | Capacitor                     | 0.1Mf                  | 2    |

| 4       | Bread Board                   |                        | 1    |

| 5       | Regulated Power Supply        | <u>+</u> 15V, Dual     | 1    |

| 6       | Function Generator            | (1Hz – 1MHz.)          | 1    |

| 7       | Cathode Ray Oscilloscope      | 20 / 40MHz, Dual Trace | 1    |

| 8       | Connecting Wires & CRO Probes |                        |      |

#### **THEORY:**

An improved filter response can be obtained by using a Second order Active Filter. A second order filter consists of two RC pairs and has a roll-off rate of -40 dB/decade. A general second order filter (Sallen Kay filter) is used to analyze different LP, HP, BP and BSF. A first order filter can be converted to second order type using an additional RC network as shown in circuit diagram. The cut off frequency  $f_L$  for the filter is now decided by R and C. The gain of the filter is usual decided by op-amp i.e. the resistance R3 and Rf.

# **DESIGN & CALCULATIONS IF ANY:**

Given:

$$f_L = 1 \text{ KHz} = 1/(2\pi RC)$$

Let C = 0.1

$$\mu$$

F, R = 1.6 K $\Omega$

For n = 2,  $\alpha$  (damping factor) = 1.414,

Pass Band Gain =  $Ao = 3 - \alpha = 3 - 1.414 = 1.586$ .

Transfer function of second order Butter worth HPF as:

$$H(s) = \frac{1.586}{S2 + 1.414 s + 1}$$

Now Ao =

$$1 + (Rf/R1) = 1.586 = 1 + 0.586$$

Let  $Ri = 10 \text{ K}\Omega$ , then  $Rf = 5.86 \text{ K}\Omega$

# **CIRCUIT DIAGRAM:**

#### SECOND ORDER ACTIVE HIGHPASS FILTER CIRCUIT DIAGRAM

# **MODEL GRAPH:**

| Sl.No. | Frequency (Hz) | Vout (V) | Gain = Vo / Vin | Gain in dB = 20 log Gain |

|--------|----------------|----------|-----------------|--------------------------|

| 1      |                |          |                 |                          |

| 2      |                |          |                 |                          |

| 3      |                |          |                 |                          |

| 4      |                |          |                 |                          |

| 5      |                |          |                 |                          |

| 6      |                |          |                 |                          |

| 7      |                |          |                 |                          |

| 8      |                |          |                 |                          |

| 9      |                |          |                 |                          |

| 10     |                |          |                 |                          |

| 11     |                |          |                 |                          |

| 12     |                |          |                 |                          |

| 13     |                |          |                 |                          |

| 14     |                |          |                 |                          |

| 15     |                |          |                 |                          |

#### **PROCEDURE:**

- 1. Construct the circuit as per Circuit diagram shown in figure.

- 2. Select the Sine waveform in Function Generator and set fixed amplitude and fixed frequency say 1V (p-p) and 1 KHz respectively.

- 3. Observe the output waveform for different frequency ranges (start from 100 Hz to beyond some value of cut of frequency, observe the output signal which pass beyond the higher cut of frequency)

- 4. Note the readings observed on CRO and find its gain for different frequency ranges.

- 5. Draw the graph for its Gain in dB Vs. Frequency and find its Cut off frequency.

# **RESULT:**

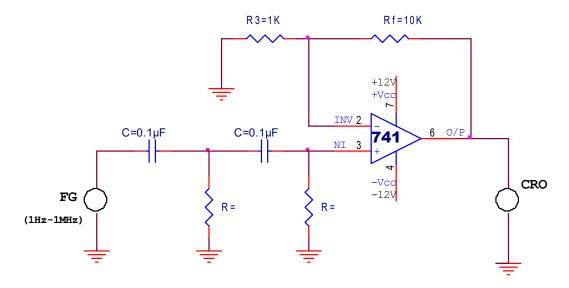

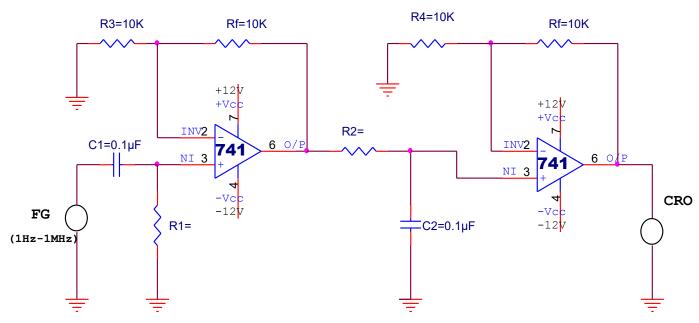

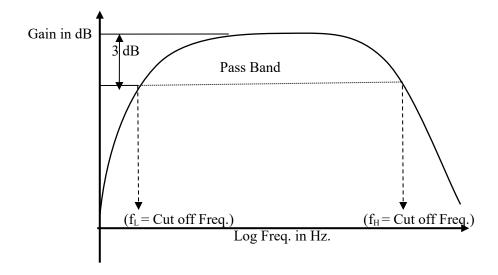

### **ACTIVE BAND PASS FILTER.**

Exp. No :

Date :

AIM:

To Design and Construct a second order low pass filter having upper cut off frequency 400 Hz and lower cut of frequency for 2 KHz using Op-amp. IC and also determine its frequency response.

APPARATUS REQUIRED:

| Sl. No: | Apparatus Name                | Range                  | Qty. |

|---------|-------------------------------|------------------------|------|

| 1       | Operational Amplifier         | IC 741                 | 1    |

| 2       | Resistors                     |                        |      |

| 3       | Capacitor                     | 0.1μF                  | 2    |

| 4       | Bread Board                   |                        | 1    |

| 5       | Regulated Power Supply        | <u>+</u> 15V, Dual     | 1    |

| 6       | Function Generator            | (1Hz – 1MHz.)          | 1    |

| 7       | Cathode Ray Oscilloscope      | 20 / 40MHz, Dual Trace | 1    |

| 8       | Connecting Wires & CRO Probes |                        |      |

#### **THEORY:**

An improved filter response can be obtained by using a Second order Active Filter. A second order filter consists of two RC pairs and has a roll-off rate of -40 dB/decade. A general second order filter (Sallen Kay filter) is used to analyze different LP, HP, BP and BSF. Band pass filter is a combination of High pass and Low pass filter. A Band pass filter is basically a frequency selector. It allows one particular band of frequencies to pass. Its pass band between two cut off frequencies  $f_H$  and  $f_L$ . The pass band which is between  $f_H$  and  $f_L$  is called Bandwidth of the filter denoted as BW.

Bandwidth =

$$f_H$$

-  $f_L$

### **DESIGN & CALCULATIONS IF ANY:**

Given:  $fH = 400Hz = 1/(2\pi RC)$

Let C = 0.1  $\mu$ F, R =

Similarly, for LPF

$fL = 2KHz = 1/(2\pi RC)$

Let C = 0.1  $\mu$ F, R =

# **CIRCUIT DIAGRAM:**

# ACTIVE BANDPASS FILTER CIRCUIT DIAGRAM

# **MODEL GRAPH:**

#### **TABULAR COLOUMN:**

Vin =

| Sl.No. | Frequency (Hz) | Vout (V) | Gain = Vo / Vin | Gain in dB = 20 log Gain |

|--------|----------------|----------|-----------------|--------------------------|

| 1      |                |          |                 |                          |

| 2      |                |          |                 |                          |

| 3      |                |          |                 |                          |

| 4      |                |          |                 |                          |

| 5      |                |          |                 |                          |

| 6      |                |          |                 |                          |

| 7      |                |          |                 |                          |

| 8      |                |          |                 |                          |

| 9      |                |          |                 |                          |

| 10     |                |          |                 |                          |

| 11     |                |          |                 |                          |

| 12     |                |          |                 |                          |

| 13     |                |          |                 |                          |

| 14     |                |          |                 |                          |

| 15     |                |          |                 |                          |

|        |                | l        |                 |                          |

# **PROCEDURE:**

- 1. Construct the circuit as per Circuit diagram shown in figure.

- 2. Select the Sine waveform in Function Generator and set fixed amplitude and fixed frequency say 1V (p-p) and 1 KHz respectively.

- 3. Observe the output waveform for different frequency ranges (start from 100 Hz to beyond some value of cut of frequency, observe the output signal which pass beyond the higher cut of frequency and it attenuates from lower cut of frequency)

- 4. Note the readings observed on CRO and find its gain for different frequency ranges.

- 5. Draw the graph for its Gain in dB Vs. Frequency and find its Cut off frequency.

# **RESULT:**

# **VIVA VOCE:**

1. State the disadvantages of passive filters?

At audio frequencies inductors becomes problematic, as the inductors become large, heavy and expensive. For low frequency application, more number of turns of wire must be used which in turn adds to the series resistance degrading inductors performance.

2. Derive the expression for voltage gain of an inverting operational amplifier?

$$A_{CL} = V_0/V_1 = -R_f/R_1$$

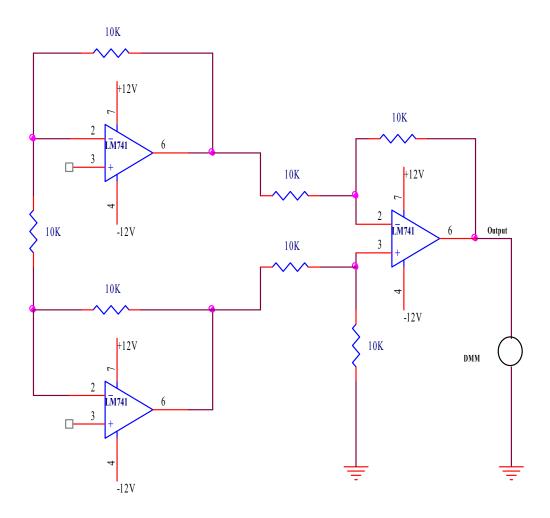

#### **INSTRUMENTATION AMPLIFIER**

Exp. No :

Date :

#### AIM:

To design and construct Instrumentation Amplifier Circuit using Op-amp IC.

# **APPAR**ATUS REQUIRED:

| Sl. No: | Apparatus Name                    | Range              | Qty. |

|---------|-----------------------------------|--------------------|------|

| 1       | Operational Amplifier             | IC 741             | 3    |

| 2       | Resistors                         | 10 ΚΩ              | 7    |

| 3       | Bread Board                       |                    | 1    |

| 4       | Regutated Power Supply (Variable) | <u>+</u> 15V, Dual | 4    |

| 5       | Multimeter                        |                    | 1    |

| 6       | Connecting Wires & CRO Probes     |                    |      |

#### THEORY:

An instrumentation amplifier is a type of <u>differential amplifier</u> that has been specifically designed to have characteristics suitable for use in measurement and <u>test equipment</u>. These characteristics include very low <u>DC</u> offset, low <u>drift</u>, low <u>noise</u>, very high <u>open-loop gain</u>, very high <u>common-mode rejection ratio</u>, and very high <u>input impedances</u>. They are used where great <u>accuracy</u> and <u>stability</u> of the <u>circuit</u> both short- and long-term are required.

The most commonly used instrumentation amplifier circuit is shown in the figure. The gain of the circuit is

$$\frac{V_{\text{out}}}{V_2 - V_1} = \left(1 + \frac{2R_1}{R_{\text{gain}}}\right) \frac{R_3}{R_2}$$

The ideal common-mode gain of an instrumentation amplifier is zero. In the circuit shown, common-mode gain is caused by mismatches in the values of the equally numbered <u>resistors</u> and by the non-zero common mode gains of the two input op-amps. Obtaining very closely matched resistors is a significant difficulty in fabricating these circuits, as is optimizing the common mode performance of the input op-amps.

# **DESIGN & CALCULATIONS IF ANY:**

$$\frac{V_{\mathrm{out}}}{V_2-V_{\underline{1}}} = \left(1+\frac{2R_1}{R_{\mathrm{gain}}}\right)\frac{R_3}{R_2}$$

Let

$$R1 = R2 = R3 = Rgain = 10 \text{ K}\Omega$$

then

$$Vout = (1+2)(V2-V1)$$

$$Vout = 3 (V2-V1)$$

# **CIRCUIT DIAGRAM:**

#### INSTRUMENTATION AMPLIFIER USING 741 IC.

# **TABULAR COLOUMN:**

| SL.NO. | INPUTS |        | OUTPUT            |                 |

|--------|--------|--------|-------------------|-----------------|

|        | V1 (V) | V2 (V) | Theoretically (V) | Practically (V) |

| 1      |        |        |                   |                 |

| 2      |        |        |                   |                 |

| 3      |        |        |                   |                 |

| 4      |        |        |                   |                 |

| 5      |        |        |                   |                 |

| 6      |        |        |                   |                 |

| 7      |        |        |                   |                 |

# **PROCEDURE:**

- 1. Construct the circuit as per Circuit diagram shown in figure.

- 2. Switch ON IC Power Supplies and apply the Input Voltages at Non-inverting input terminals.

- 3. Observe the Output Voltage using Digital Multimeter for different input voltages.

- 4. Note the readings and verify its values with theoretical calculation.

# **RESULT:**

# **CHARACTERISTICS OF PLL.**

Exp. No :

Date :

# AIM:

To construct and study the operation of PLL IC 565 and determine its Characteristics.

# **APPARATUS REQUIRED:**

| S.No | Components         | Range                    | Quantity |

|------|--------------------|--------------------------|----------|

| 1    | IC 565             | -                        | 1        |

| 2    | Resistors          | 6.8 ΚΩ                   | 1        |

| 3    | Capacitors         | 0.001 μF<br>0.1 μF, 1 μF | 1 each   |

| 4    | Function Generator | (1Hz – 1MHz.)            | 1        |

| 5    | C.R.O              | -                        | 1        |

| 6    | Dual Power Supply  | 0- 30 V                  | 1        |

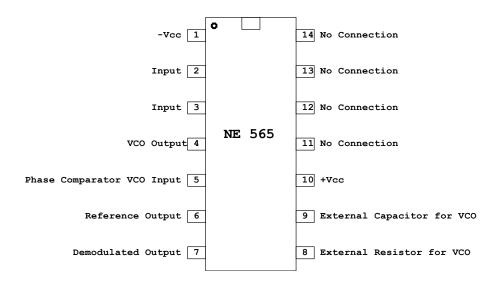

# PIN DIAGRAM (IC 565 - PLL)

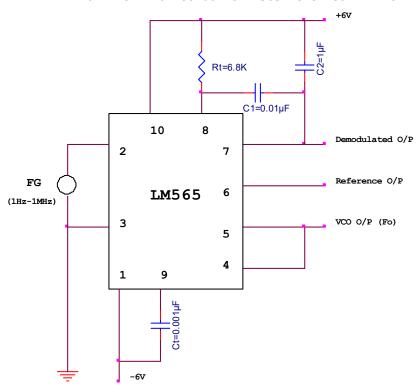

#### **CIRCUIT DIAGRAM:**

#### PLL CHARACTERISTICS USING LM565 IC CIRCUIT DIAGRAM

# **PROCEDURE:**

- The connections are given as per the circuit diagram.

- Measure the free running frequency of VCO at pin 4, with the input signal Vi set equal to zero. Compare it with the calculated value = 0.25 / (RT CT).

- Now apply the input signal of 1 VPP square wave at a 1 KHz to pin 2. Connect one channel of the scope to pin 2 and display this signal on the scope.

- Gradually increase the input frequency till the PLL is locked to the input frequency. This frequency f1 gives the lower end of the capture range. Go on increasing the input frequency, till PLL tracks the input signal, say, to a frequency f2. This frequency f2 gives the upper end of the lock range. If input frequency is increased further, the loop will get unlocked.

- Now gradually decrease the input frequency till the PLL is again locked. This is the frequency f3, the upper end of the capture range. Keep on decreasing the input frequency until the loop is unlocked. This frequency f4 gives the lower end of the lock range.

- The lock range  $\Delta fL = (f2 f4)$ . Compare it with the calculated value of  $\pm 7.8$  fo /12. Also the capture range is  $\Delta fc = (f3 f1)$ . Compare it with the calculated value of capture range.

$$\Delta fc = \pm (\Delta fL / (2\pi)(3.6)(103) C)1/$$

# **TABULAR COLOUMN:**

| INPUT WAVEFORM     |  | OUTPUT WAVEFORM                        |  |

|--------------------|--|----------------------------------------|--|

| Square wave Signal |  | Square wave Signal with Multiple Freq. |  |

| Amplitude (V)      |  | Amplitude (V)                          |  |

| Time (ms)          |  | Time (ms)                              |  |

| Frequency (Hz)     |  | Frequency (Hz)                         |  |

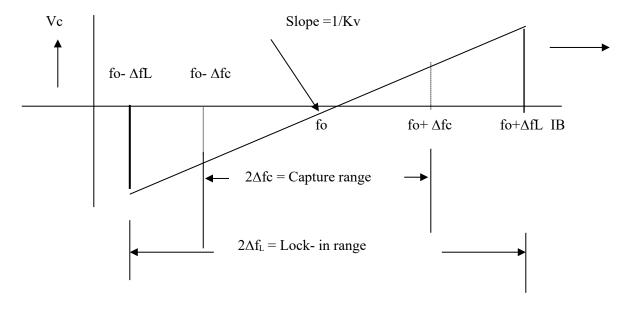

# **MODEL GRAPH**

# **RESULT:**

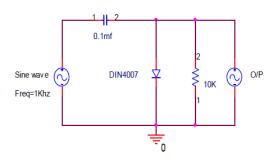

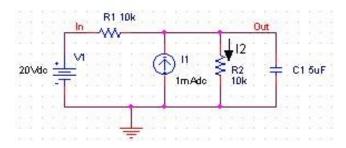

#### FREQUENCY MULTIPLIER USING PLL.

Exp. No :

Date :

AIM:

To construct and study the operation of frequency multiplier using IC 565.

# **APPARATUS REQUIRED:**

| S.No | Components                  |                                        |          |

|------|-----------------------------|----------------------------------------|----------|

|      |                             | Range                                  | Quantity |

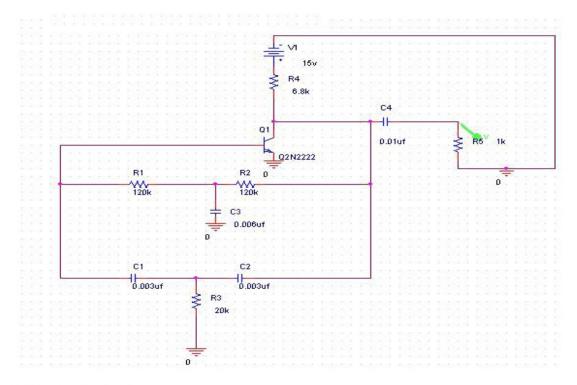

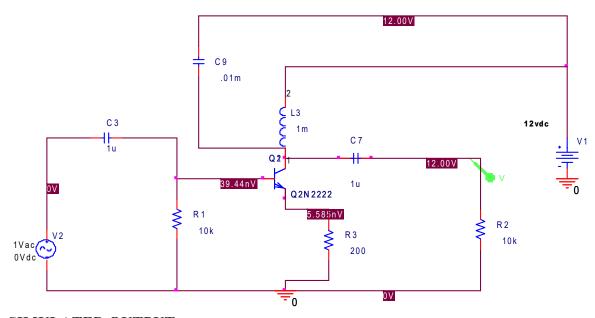

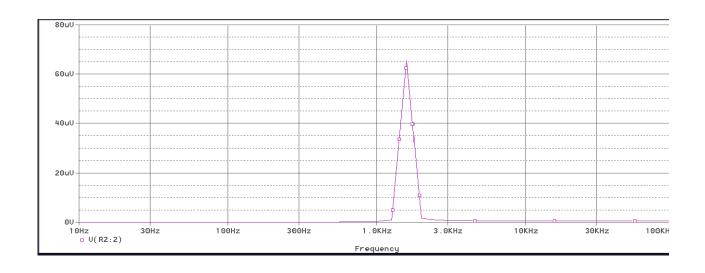

| 1    | IC 565,IC 7490,2N2222       | -                                      | 1        |

| 2    | Resistors                   | $20 \text{ K}\Omega, 2\text{k}\Omega,$ | 1        |

|      |                             | $4.7$ k $\Omega$ , $10$ k $\Omega$     |          |

| 3    | Capacitors                  | 0.001 μF, 10 μF                        | 1 each   |

| 4    | FunctionGenerator (Digital) | 1 Hz – 2 MHz                           | 1        |

| 5    | C.R.O                       | -                                      | 1        |

| 6    | Dual Power Supply           | 0- 30 V                                | 1        |

| 7.   |                             |                                        |          |

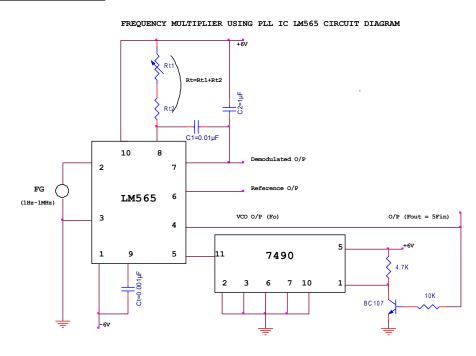

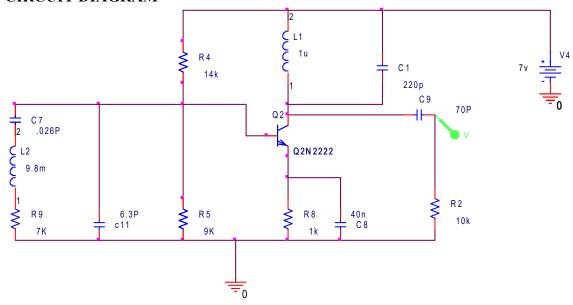

# **THEORY:**

The circuit diagram of a Frequency multiplier using PLL is shown in Figure. A divide by N network is inserted between VCO Output and Phase comparator input. In the locked stste, the VCO output frequency fo is given by,

$$f_0 = N f_S$$

The multiplication factor can be obtained by selecting a proper scaling factor N of the counter. Frequency multiplication can also be obtained by using PLL in its harmonic locing mode.

The output of VCO is given by,

$f_0 = f_S / m$

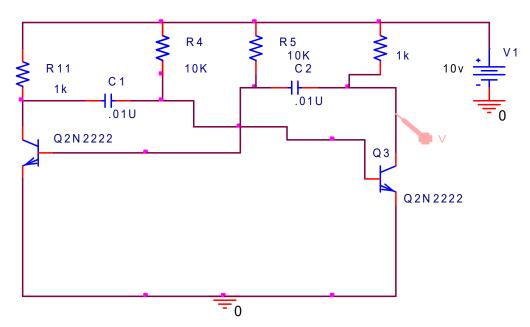

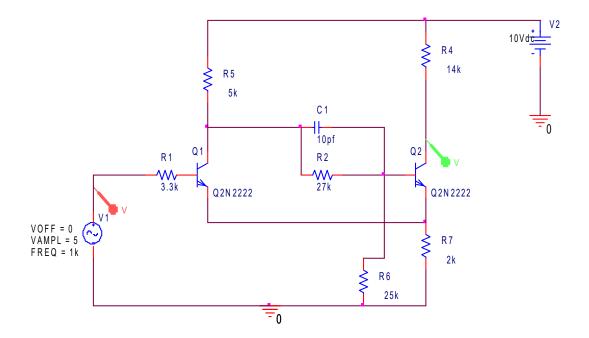

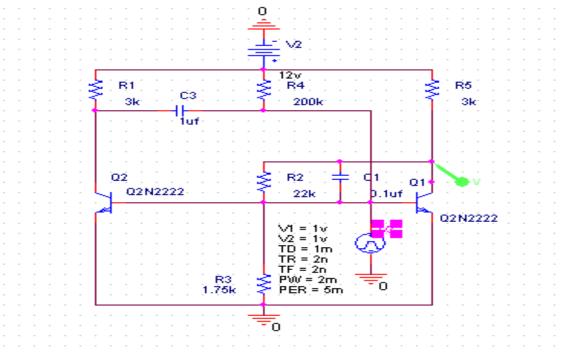

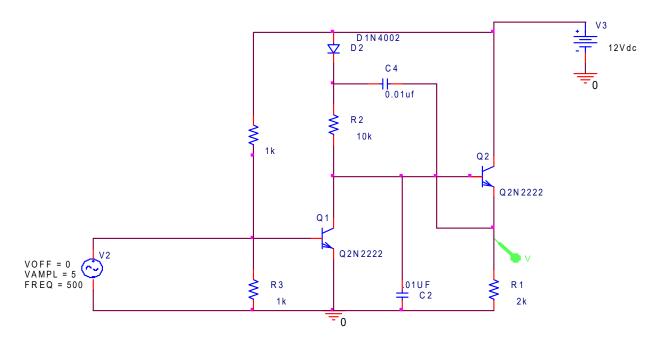

# **CIRCUIT DIAGRAM:**

EC3462-Linear Integrated Circuits Lab

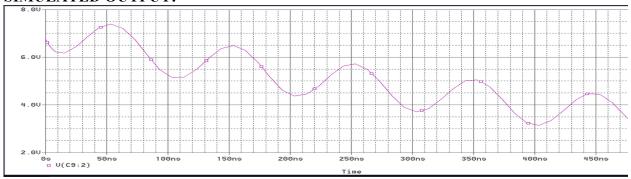

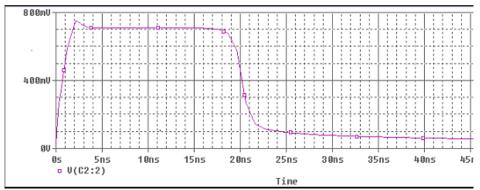

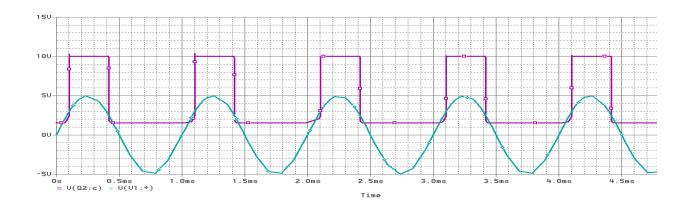

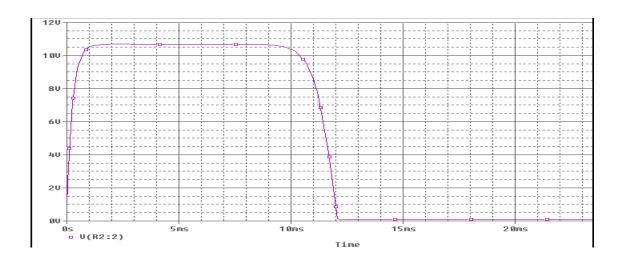

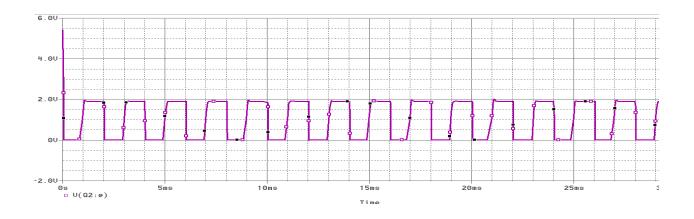

#### **MODEL GRAPH:**

# **TABULAR COLOUMN:**

| INPUT WAVEFORM     |  | OUTPUT WAVEFORM                              |  |

|--------------------|--|----------------------------------------------|--|

| Square wave Signal |  | Square wave Signal (Multiples of input freq) |  |

| Amplitude (V)      |  | Amplitude (V)                                |  |

| Time Period (ms)   |  | Time Period (ms)                             |  |

# **PROCEDURE:**

- 1. The connections are given as per the circuit diagram.

- 2. The circuit uses a 4- bit binary counter 7490 used as a divide-by-5 circuit.

- 3. Measure the free running frequency of VCO at pin 4, with the input signal Vi set equal to zero. Compare it with the calculated value = 0.25 / (RT CT).