# JEPPIAAR ENGINEERING COLLEGE DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

# **VISION OF INSTITUTION**

To build Jeppiaar Engineering College as an institution of academic excellence in technology and management education, leading to become a world class University.

# **MISSION OF INSTITUTION**

- To excel in teaching and **learning, research and innovation** by promoting the principles of scientific analysis and creative thinking.

- To participate in the production, **development**, **dissemination of knowledge** and interact with **national and international communities**.

- To equip students with ethical **values, and life skills** that would enrich their lives and enable them to meaningfully contribute to the **progress of the society.**

- To prepare students for higher studies and lifelong learning, enrich them with the practical and entrepreneurial skills necessary to excel as future professionals and contribute to Nation's economy.

# **PROGRAM OUTCOMES (POs)**

- **1** Engineering knowledge: Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

- **2 Problem analysis**: Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

- **3 Design/development of solutions**: Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations

- **4 Conduct investigations of complex problems**: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

- **5** Modern tool usage: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

- **6** The engineer and society: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

- 7 Environment and sustainability: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

- **8** Ethics: Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

- **9** Individual and team work: Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

- **10 Communication**: Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

- **11 Project management and finance**: Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

**12** Life-long learning: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

# VISION OF THE DEPARTMENT

The Department of Electrical and Electronics Engineering strives to be a Centre of Excellence in education and technical research, in the endeavour of which the Department will continually update the teaching methodologies, progress in the emerging technologies and continue to play a vital role in the development of the society.

# MISSION OF THE DEPARTMENT

| M1 | To develop the ability to <b>learn</b> and work creatively that would enhance the ability of both students and faculty to do <b>innovative research</b> .                                                                                                |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M2 | To <b>create</b> and maintain state-of-the art facilities which provide students and faculty with opportunities to analyse, apply and <b>disseminate knowledge globally</b> .                                                                            |

| M3 | To impart the knowledge in essential interdisciplinary fields which will enhance the <b>interpersonal skills</b> , team work, professional <b>ethics</b> and make them work effectively for their own benefit and the <b>betterment of the society</b> . |

| M4 | Prepare students for <b>lifelong learning</b> of theoretical and <b>practical concepts</b> to face intellectual, <b>economical</b> and career challenges.                                                                                                |

# PROGRAM EDUCATIONAL OBJECTIVES (PEOs)

| <b>PEO 01</b> | Strengthen the knowledge in Electrical and Electronics Engineering to enable them         |

|---------------|-------------------------------------------------------------------------------------------|

| I EO UI       | work for modern industries by promoting energy conservation and sustainability.           |

| <b>PEO 02</b> | Enrich analytical, creative and critical logical reasoning skills to solve problems faced |

| FEO 02        | by emerging domains of electrical and electronics engineering industries worldwide.       |

|               | Develop effective communication and inter-personal skills to work with enhanced team      |

| <b>PEO 03</b> | spirit in multidisciplinary projects with a broader ethical, professional, economical and |

|               | social perspective.                                                                       |

| <b>PEO 04</b> | Prepare the students either to establish start ups or to pursue higher education at       |

|               | reputed institutions.                                                                     |

# PROGRAM SPECIFIC OUTCOME (PSOs)

| PSO 1 | <b>Professional Skills:</b><br>Apply the knowledge of Mathematics, Science and Engineering to solve real time problems in the field of <b>Power Electronics, Electrical Drives, Power Systems, Control Systems and Instrumentation</b> .                       |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSO 2 | <b>Research and Innovation:</b><br>Analyze and synthesize circuits by solving complex engineering problems to obtain the <b>optimal solution</b> using effective software tools and hardware prototypes in the field of robotics and renewable energy systems. |

| PSO 3 | <b>Product development:</b><br>Develop concepts and <b>products</b> by applying ideas of electrical domain into other diversified engineering domains.                                                                                                         |

# **EE8351 DIGITAL LOGIC CIRCUITS**

# **OBJECTIVES:**

$\Box$  To study various number systems and simplify the logical expressions using Boolean functions

$\Box$  To study combinational circuits

□ To design various synchronous and asynchronous circuits.

□ To introduce asynchronous sequential circuits and PLDs

□ To introduce digital simulation for development of application oriented logic circuits.

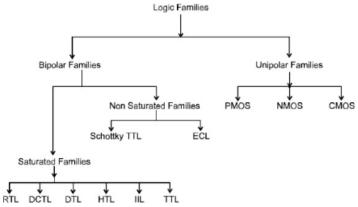

**UNIT I NUMBER SYSTEMS AND DIGITAL LOGIC FAMILIES** 6+6 Review of number systems, binary codes, error detection and correction codes (Parity and Hamming code) - Digital Logic Families -comparison of RTL, DTL, TTL, ECL and MOS families -operation, characteristics of digital logic family.

# **UNIT II COMBINATIONAL CIRCUITS**

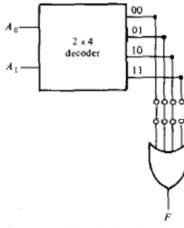

Combinational logic - representation of logic functions-SOP and POS forms, K-map representations - minimization using K maps - simplification and implementation of combinational logic - multiplexers and de multiplexers - code converters, adders, subtractors, Encoders and Decoders.

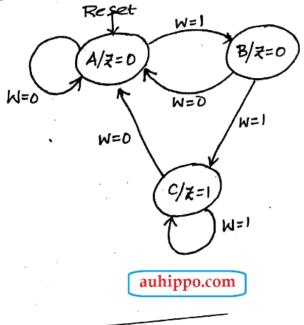

# **UNIT III SYNCHRONOUS SEQUENTIAL CIRCUITS**

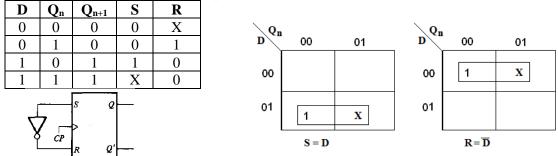

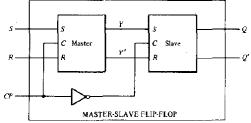

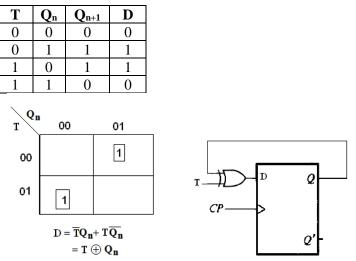

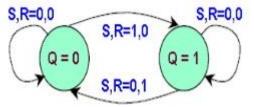

Sequential logic- SR, JK, D and T flip flops - level triggering and edge triggering - counters asynchronous and synchronous type - Modulo counters - Shift registers - design of synchronous sequential circuits - Moore and Melay models- Counters, state diagram; state reduction; state assignment.

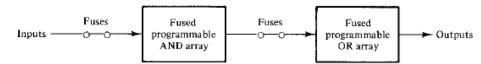

#### UNIT IV **ASYNCHRONOUS** SEQUENTIAL **CIRCUITS** AND PROGRAMMABILITY LOGIC DEVICES 6+6

Asynchronous sequential logic circuits-Transition tability, flow tability-race conditions, hazards & errors in digital circuits; analysis of asynchronous sequential logic circuits introduction to Programmability Logic Devices: PROM - PLA - PAL, CPLD-FPGA.

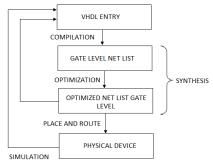

# UNIT V VHDL

RTL Design - combinational logic - Sequential circuit - Operators - Introduction to Packages - Subprograms - Test bench. (Simulation / Tutorial Examples: adders, counters, flip flops, Multiplexers & De multiplexers).

# **TOTAL : 60 PERIODS**

# **TEXT BOOKS:**

1. James W. Bignel, Digital Electronics, Cengage learning, 5th Edition, 2007.

2. M. Morris Mano, 'Digital Design with an introduction to the VHDL', Pearson Education, 2013.

3. Comer "Digital Logic & State Machine Design, Oxford, 2012.

# REFERENCES

1. Mandal, "Digital Electronics Principles & Application, McGraw Hill Edu, 2013.

2. William Keitz, Digital Electronics-A Practical Approach with VHDL, Pearson, 2013.

3. Thomas L.Floyd, 'Digital Fundamentals', 11th edition, Pearson Education, 2015.

4. Charles H.Roth, Jr, Lizy Lizy Kurian John, 'Digital System Design using VHD, Cengage, 2013.

5. D.P.Kothari, J.S.Dhillon, 'Digital circuits and Design', Pearson Education, 2016.

6+6

6+6

6+6

#### Course code& Name: **EE8351 & Digital Logic Circuits** Degree/Programme: **B.E/EEE** Semester: **III** Duration: **DEC – APRIL 2018** Name of the Staff:

Section: **A**, **B** Regulation: **2017/AUC**

#### AIM

• To understand and analyse the digital electronic circuits.

#### **OBJECTIVES**

- To study various number systems, simplify the logical expressions using Boolean functions

- To study implementation of combinational circuits

- To design various synchronous and asynchronous circuits.

- To introduce asynchronous sequential circuits and PLCs

- To introduce digital simulation for development of application oriented logic circuits

| C2 2.1 | Recollecting the various number systems and simplifications using mathematical expression and understand the concepts of digital logic families |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| C2 2.2 | Ability to design and implementation of combinational logic circuits                                                                            |

| C2 2.3 | Ability to design and implementation of combinational logic circuits                                                                            |

| C2 2.4 | Design of asynchronous sequential circuits and describe the operation of Programmable Logic Devices                                             |

| C2 2.5 | Ability to understand the digital simulation techniques for application oriented logic circuits using VHDL coding.                              |

| EE8351 | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO 12 | PSO1 | PSO2 | PSO3 |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|-------|------|------|------|

| C2 2.1 | 3   | 3   | 1   | 1   | -   | -   | -   | -   | -   | 2    | -    | 3     | 3    | 1    | 3    |

| C2 2.2 | 3   | 3   | 3   | 2   | -   | -   | -   | -   | -   | 2    | -    | 3     | 3    | 1    | 3    |

| C2 2.3 | 3   | 3   | 3   | 2   | -   | -   | -   | -   | -   | 2    | -    | 3     | 3    | 1    | 3    |

| C2 2.4 | 3   | 3   | 3   | 1   | -   | -   | -   | -   | -   | 2    | -    | 3     | 3    | 1    | 3    |

| C2 2.5 | 3   | 2   | 1   | 1   | 3   | -   | -   | -   | -   | 2    | -    | 3     | 3    | 1    | 3    |

| UNIT-I  | NUMBER SYSTEMS AND DIGITAL LOGIC FAMILIES                                                  |                 | Target Period :9               |                        |                       |                    |

|---------|--------------------------------------------------------------------------------------------|-----------------|--------------------------------|------------------------|-----------------------|--------------------|

| Sl N o  | Contents                                                                                   | CO<br>Statement | Book<br>Reference &<br>Page No | Delivery<br>method     | Delive<br>ry<br>Perio | Knowledge<br>Level |

| 1       | Review of number systems                                                                   | C2 2.1          | T1[11]                         | Chalk & board<br>/ PPT |                       | R & U              |

| 2       | Binary codes, Error detection codes                                                        | C2 2.1          | R4[62,75]                      | Chalk & board<br>/ PPT | 1                     | R & U              |

| 3       | Error correction codes (Parity and Hamming code)                                           | C2 2.1          | R4[79]                         | Chalk & board<br>/ PPT | 1                     | R, U, A            |

| 4       | Digital Logic Families: RTL-operation                                                      | C2 2.1          | T1[131]<br>R9[7.2]             | Chalk & board<br>/ PPT | 1                     | R, U               |

| 5       | DTL, ECL -operation                                                                        |                 | T1[134]<br>R9[7.28]            | Chalk & board<br>/ PPT | 1                     | R, U               |

| 6       | TTL -operation                                                                             | ()))            | T1[136]<br>R9[7.6]             | Chalk & board<br>/ PPT | 1                     | R,U                |

| 7       | MOS families -operation                                                                    |                 | T1[147]<br>R9[7.19]            | Chalk & board<br>/ PPT | 1                     | R,U                |

| 8       | Comparison of RTL, DTL, TTL, ECL and MOS families, characteristics of digital logic family | C2 2.1          | T1[151]<br>R9[7.31]<br>R9[7.2] | Chalk & board<br>/ PPT | 2                     | R,U                |

| UNIT II | COMBINATION                                                                                |                 |                                | Tar                    | get Per               | iods:9             |

| SI No   | Contents                                                                                   | CO<br>Statement | Book<br>Reference<br>& Page No | Delivery<br>method     | Delive<br>ry Hrs      | Knowledge<br>Level |

| 1       | Combinational logic circuits                                                               | C2 2.2          | T1[53]<br>R9[1.2]              | Chalk & board<br>/ PPT | 1                     | R, U,A             |

| 2       | Representation of logic functions                                                          | C2 2.2          | T1[57]<br>R9[1.4]              | Chalk & board<br>/ PPT | 1                     | R, U, A, An        |

| 3       | SOP and POS forms                                                                          | C2 2.2          | T1[60,64]<br>R9[1.8]           | Chalk & board<br>/ PPT | 1                     | R, U, A, An        |

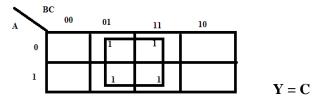

| 4       | K-map representations                                                                      | C2 2.2          | T1[76]<br>R9[1.18]             | Chalk & board<br>/ PPT | 1                     | R, U, A, An        |

| 5       | Minimization using K maps                                                                  | C2 2.2          | T1[78]<br>R9[1.56]             | Chalk & board<br>/ PPT | 1                     | R, U, A, An        |

| 6       | Simplification and implementation of combinational logic                                   | C2 2.2          | T1[89]<br>R9[1.69]             | Chalk & board<br>/ PPT | 1                     | R, A, An           |

| 7       | Multiplexers and demultiplexers                                                            | C2 2.2          | T1[227]<br>R9[2.40]            | Chalk & board<br>/ PPT | 1                     | R, U,A,An          |

| 8       | Code converters                                                                            | C2 2.2          | T1[249]<br>R9[2.19]            | Chalk & board<br>/ PPT | 1                     | R, U,A,An          |

| 9       | Adders, subtractors, Encoders, Decoders                                                    | C2 2.2          | T1[214]<br>R9[2.5]             | Chalk & board<br>/ PPT | 1                     | R, U,A,An          |

| UNIT I  | I SYNCHRONOUS S                                                                            | EQUENT          | <u>'IAL CIRCUIT</u>            | <u>'S Ta</u>           | rget Pe               | riods: 9           |

| SI No   | Contents                                                                                   | CO<br>Statement | Book<br>Reference &<br>Page No | Delivery<br>method     | Delive<br>ry Hrs      | Knowledge<br>Level |

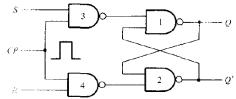

| 1       | Sequential logic- SR, JK flip flops                                                        | C2 2.3          | T1[312] R9[3.2]                | Chalk &<br>board / PPT | 1                     | R, U, A,An         |

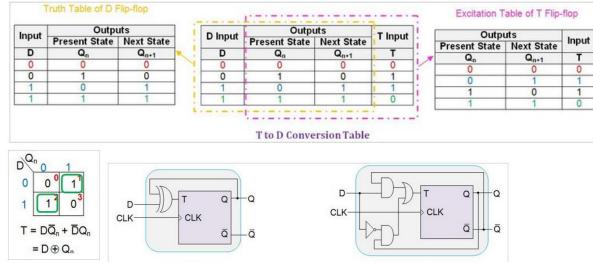

|         | D and T flip flops –working Principles, Truth                         |                 | T1[326]                           | Chalk &                |                  | R, U, A, An        |

|---------|-----------------------------------------------------------------------|-----------------|-----------------------------------|------------------------|------------------|--------------------|

| 2       | table,Excitation Table                                                | C2 2.3          | R9[3.9]                           | board / PPT            | 1                |                    |

| 3       | Level triggering and edge triggering of flip flops                    | C2 2.3          | T1[335]<br>R9[3.3]                | Chalk &<br>board / PPT | 1                | R, U, A            |

| 4       | Counters - asynchronous type                                          | C2 2.3          | T1[390]<br>R9[4.59]               | Chalk &<br>board / PPT | 1                | R, U,A,An          |

| 5       | Counters - synchronous type                                           | C2 2.3          | T1[400]<br>R9[4.44]               | Chalk & board / PPT    | 1                | R, U, A,An         |

| 6       | Modulo counters                                                       | C2 2.3          | T1[395]<br>R9[4.62]               | Chalk & board / PPT    | 1                | R, U, A, An        |

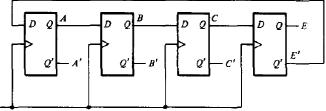

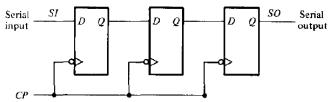

| 7       | Shift registers                                                       | C2 2.3          | T1[385]                           | Chalk &<br>board / PPT | 1                | R, U, A, An        |

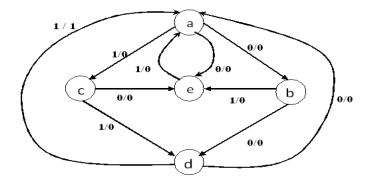

| 8       | Design of synchronous sequential circuits –<br>Moore and Melay models | C2 2.3          | T1[353]<br>R9[4.2]                | Chalk &<br>board / PPT | 1                | R, U, A,An         |

| 9       | Counters, state diagram; state reduction; state assignment.           |                 | T1[355]<br>R9[4.5]                | Chalk &<br>board / PPT | 1                | R,U,A              |

| UNIT IV | 7 Asynchronous Sequential Circuits and Prog                           | rammabl         | e Logic Devices                   | 5 Target l             | Periods          | :9                 |

| Sl No   | Contents                                                              | CO<br>Statement | Book<br>Reference &<br>Page No    | Delivery<br>method     |                  | Knowledge<br>Level |

| 1       | Asynchronous sequential logic circuits                                | C2 2.4          | T1[442] R9[5.2                    | Chalk & board / PPT    | 1                | R, U,A,An          |

| 2       | Transition table, flow table                                          | C2 2.4          | T1[459]<br>R9[5.24]               | Chalk &<br>board / PPT | 1                | R, U, A, An        |

| 3       | Race conditions                                                       | C2 2.4          | T1[456]<br>R9[5.30]               | Chalk &<br>board / PPT | 1                | R, U, A, An        |

| 4       | Hazards in digital circuits                                           | C2 2.4          | T1[467]<br>R9[B.2]                | Chalk &<br>board / PPT | 1                | R, U, A, An        |

| 5       | Errors in digital circuits                                            | C2 2.4          | T1[467]                           | Chalk &<br>board / PPT | 1                | R, U, A, An        |

| 6       | Analysis of asynchronous sequential logic circuits                    | C2 2.4          | T1[448] R9[5.4                    | Chalk & board / PPT    | 1                | R, U, A, An        |

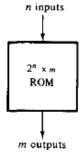

| 7       | Introduction to Programmable Logic Devices:<br>PROM                   | C2 2.4          | R4[582] R9[6.5                    | ] Chalk & board / PPT  | 1                | R, U               |

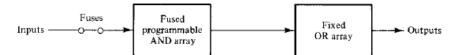

| 8       | PLA,PAL                                                               | 1 1 1 4         | R4[608]<br>R9[6.19]               | Chalk & board / PPT    | 1                | R, U               |

| 9       | CPLD,FPGA                                                             | C2 2.4          | T1[509]<br>R9[6.33]               | Chalk &<br>board / PPT | 1                | R, U               |

| UNIT V  | VHDL                                                                  |                 |                                   | et Periods: 9          | )                |                    |

| Sl No   | Contents                                                              | CO<br>Statement | Book<br>Reference<br>& Page<br>No | Delivery<br>method     | Delive<br>ry Hrs |                    |

| 1       | RTL Design                                                            |                 |                                   | halk & board /<br>PPT  | 1                | R, U,              |

| 2       | Combinational logic circuit                                           | C2 2.5          |                                   | halk & board /<br>PPT  | 1                | R, U               |

| 3       | Sequential circuit                                                    | C2 2.5          |                                   | halk & board /<br>PPT  | 1                | R, U               |

| 4       | Operators                                                             |                 | R5[76] CI<br>R9[8.16]             | halk & board /<br>PPT  | 1                | R, U               |

| 5  | Introduction to Packages                                     | C2 2.5 | R5[76]<br>R9[8.3]   | Chalk & board /<br>PPT | 1 | R, U     |

|----|--------------------------------------------------------------|--------|---------------------|------------------------|---|----------|

| 6  | Subprograms                                                  | C2 2.5 | R9[8.69]            | Chalk & board /<br>PPT | 1 | R, U     |

| 7  | Test bench, Revision                                         | C2 2.5 | R9[8.115]           | Chalk & board /<br>PPT | 1 | R, U     |

| 8  | Simulation /Tutorial Examples: adders                        | C2 2.5 | R9[8.98]            | Chalk & board /<br>PPT | 1 | R, U, A, |

| 9  | Simulation /Tutorial Examples: counters                      | C2 2.5 | R9[8.86]            | Chalk & board /<br>PPT | 1 | R, U, A, |

| 10 | Simulation /Tutorial Examples: flip-flops                    | C2 2.5 | R5[44]<br>R9[8.106] | Chalk & board /<br>PPT | 1 | R, U, A, |

| 11 | Simulation /Tutorial Examples: FSM                           | C2 2.5 | R9[8.94]            | Chalk & board /<br>PPT | 1 | R, U, A, |

| 12 | Simulation /Tutorial<br>Examples:Multiplexers/Demultiplexers | C2 2.5 | R5[54]              | Chalk & board /<br>PPT | 1 | R, U, A, |

#### Books: Text (T) / Reference(R):

|      | Book |                                                    |                          |                         |      |

|------|------|----------------------------------------------------|--------------------------|-------------------------|------|

| S.No | No   | Title of the Book                                  | Author                   | Publisher               | Year |

| 1    | T1   | Digital Systems – Principles and Design            | Raj Kamal                | Pearson Edison, 2nd     | 2007 |

|      |      |                                                    |                          | edition                 |      |

| 2    | T2   | Digital Design with an introduction to the VHDL    | M. Morris Mano           | Pearson Education       | 2013 |

| 3    | T3   | Digital Logic & State Machine Design,              | Comer                    | Oxford                  | 2012 |

| 4    | R1   | Digital Electronics Principles & Application       | Mandal                   | McGraw Hill Edu         | 2013 |

| 5    | R2   | Digital Electronics-A Practical Approach with VHDL | William Keitz            | Pearson                 | 2013 |

| 6    | R3   | Digital Fundamentals                               | Floyd and Jain           | 8th edition, Pearson    | 2003 |

|      |      |                                                    |                          | Education               |      |

| 7    | R4   | Fundamentals of Digital Circuits                   | Anand Kumar              | PHI                     | 2013 |

| 8    | R5   | Digital System Design using VHDL                   | Charles H.Roth, Jr, Lizy | Cengage                 | 2013 |

|      |      |                                                    | Lizy Kurian John         |                         |      |

| 9    | R6   | Digital Logic, Application & Design                | John M. Yarbrough        | Thomson                 | 2002 |

| 10   | R7   | VHDL Basics to Programming                         | Gaganpreet Kaur          | Pearson                 | 2013 |

| 11   | R8   | HDL Programming Fundamental, VHDL& Verilog         | Botros                   | Cengage                 | 2013 |

| 12   | R9   | Digital Logic Circuits                             | A.P.Godse &              | Technical               | 2014 |

|      |      |                                                    | D.A.Godse                | Publications            |      |

| 13   | R10  | Digital Circuits and Design                        | S.Salivahanan &          | Vikas Publication       | 2008 |

|      |      |                                                    | S. Arivazhzgan           | 3 <sup>rd</sup> Edition |      |

| Comments Given by the<br>Scrutinizing Committee Members |  |

|---------------------------------------------------------|--|

| Signature of the Scrutinizing                           |  |

| Signature of the HOD                                    |  |

# EE8351 DIGITAL LOGIC CIRCUITS

# UNIT – I

#### NUMBER SYSTEMS AND DIGITAL LOGIC FAMILIES

#### PART-A

# 1. What is the different classification of binary codes?

- Weighted codes

- Non weighted codes

- Reflective codes

- Sequential codes

- Alphanumeric codes

- Error Detecting and correcting codes.

# 2. What are the needs for binary codes?

- a. Code is used to represent letters, numbers and punctuation marks.

- b. Coding is required for maximum efficiency in single transmission.

- c. Binary codes are the major components in the synthesis (artificial generation) of speech and video signals.

- d. By using error detecting codes, errors generated in signal transmission can be detected.

- e. Codes are used for data compression by which large amounts of data are transmitted in very short duration of time.

#### 3. What are weighed codes? Give examples (*NOV/DEC 2012*)

The weighed codes are the codes that have assigned weights or values for each bit position. A code in which each bit position has a certain numeric value assigned. Several such codes exist, such as 8-4-2-1, 7-4-2-1, 6-3-1 -1, Excess – 3 code.

#### 4. What are cyclic codes? (*APR/MAY 2013*)

An (n, k) linear code C is called a cyclic code if any cyclic shift of a codeword is another codeword. That is,

$$\mathbf{if} \quad \overline{c} = (c_{\theta}, c_1, \cdots, c_{n-1}) \in C$$

then

$$\bar{c}^{(1)} = (c_{n-1}, c_{\theta}, c_1, \cdots, c_{n-2}) \in C$$

# 5. What are self complementing codes?

These are the codes whose arithmetic and logic complements are the same. Example: Excess - 3 code, 2421 code

6. What are BCD codes? A special binary code used to directly represent the decimal characters. Each four bit value in BCD represents a single decimal character.

# 7. What are alphanumeric codes? A binary code used to represent the alphabets, numbers and punctuation marks as well as control characters for controlling a printer or display. Eg – ASCII, EBCD

8. What is an Excess – 3 code?

A self complementing code used to represent BCD numbers. It is self complementing because the 1's complement is also the 9's complement of the BCD number. It is widely used in BCD arithmetic circuits.

**Example:** 1000 of 8421 = 1011 in Excess-3

9. What is a Gray code? (or) What is a unit distance code? Give an example (NOV/DEC 2015)

A reflective, unit distance code where only one bit position changes for each adjacent change in value.

# 10. Define radix or base.

The number of characters in the characters set of a positional number system. Decimal numbers have a base of 10, binary numbers have a base of 2. Base and radix are used interchangeably.

#### 11. List the advantages and disadvantages of BCD code?

12. The advantages of BCD code are

- a. Any large decimal number can be easily converted into corresponding binary number

- b. A person needs to remember only the binary equivalents of decimal number from 0 to 9.

- c. Conversion from BCD into decimal is also very easy.

The disadvantages of BCD code are

- a. The code is least efficient. It requires several symbols to represent even small numbers.

- b. Binary addition and subtraction can lead to wrong answer.

- c. Special codes are required for arithmetic operations.

- d. This is not a self-complementing code.

- e. Conversion into other coding schemes requires special methods.

# 13. What is meant by self-complementing code?

A self-complementing code is the one in which the members of the number system complement on themselves. This requires the following two conditions to be satisfied.

- a. The complement of the number should be obtained from that number by replacing 1s with 0s and 0s with 1s.

- b. The sum of the number and its complement should be equal to decimal 9. Example of a self-complementing code is

- 1. 2-4-2-1 code.

- 2. Excess-3 code.

- 3. BCD code

# 14. Mention the advantages of ASCII code?

The following are the advantages of ASCII code

- a. There are 27 =128 possible combinations. Hence, a large number of symbols, alphabets etc.., can be easily represented.

- b. There is a definite order in which the alphabets, etc.., are assigned to each code word.

- c. The parity bits can be added for error-detection and correction.

# 15. What are the disadvantages of ASCII code?

#### The disadvantages of ASCII code are

- a. The length of the code is larger and hence more bandwidth is required for transmission.

- b. With more characters and symbols to represent, this is not completely sufficient.

#### 16. What is a reflective code?

A code is said to be reflective when code for 9 is complement for the code for 0, and so is for 8 and 1 codes, 7 and 2, 6 and 3, 5 and 4. Codes 2421, 5211, gray and excess-3 are reflective, whereas the 8421 code is not.

#### **17. What is sequential code?**

A code is said to be sequential when two subsequent codes, seen as numbers in binary representation, differ by one. This greatly aids mathematical manipulation of data. The 8421 and Excess-3 codes are sequential, whereas the 2421 and 5211 codes are not.

# 18. What is meant by parity bit?

Parity bit is an extra bit included with a binary message to make the number of 1's either odd or even. The message, including the parity bit is transmitted and then checked at the receiving and for errors.

#### **19.** What is even and odd parity?

(NOV/DEC 2011)

A parity bit is an extra bit included with a message to make the total number of 1's either even or odd. Consider the following two characters and their even and odd parity:

|                   | With even parity | With odd parity |

|-------------------|------------------|-----------------|

| ASCII A = 1000001 | 01000001         | 11000001        |

| ASCII T = 1010100 | 11010100         | 01010100        |

In each case we add an extra bit in the left most position of the code to produce an even number of 1's in the character for even parity or an odd number of 1's in the character for odd parity. The parity bit is helpful in detecting errors during the transmission of information from one location to another.

#### 20. State the associative property of Boolean algebra.

The associative property of Boolean algebra states that the OR ing of several variables results in the same regardless of the grouping of the variables. The associative property is stated as follows: A + (B+C) = (A+B) + C

#### 21. State the commutative property of Boolean algebra.

The commutative property states that the order in which the variables are OR ed makes no difference. The commutative property is: A+B=B+A

# 22. State and prove the distributive property of Boolean algebra.(NOV/DEC 2012)

The distributive property states that AND ing several variables and OR ing the result with a single variable is equivalent to OR ing the single variable with each of the several variables and then AND ing the sums. The distributive property is: A+BC=(A+B)(A+C)

| x | У | z | y+z | $x \cdot [y + z]$ | <i>x</i> ∙ <i>y</i> | χ·Ζ | $(x\cdot y) + (x\cdot z)$ |

|---|---|---|-----|-------------------|---------------------|-----|---------------------------|

| 0 | 0 | 0 | 0   | 0                 | 0                   | 0   | 0                         |

| 0 | 0 | 1 | 1   | 0                 | 0                   | 0   | 0                         |

| 0 | 1 | 0 | 1   | 0                 | 0                   | 0   | 0                         |

| 0 | 1 | 1 | ł   | 0                 | 0                   | 0   | 0                         |

| 1 | 0 | 0 | 0   | 0                 | 0                   | 0   | 0                         |

| 1 | 0 | 1 | 1   | i                 | 0                   | 1   | 1                         |

| 1 | 1 | 0 | 1   | L                 | 1                   | 0   | 1                         |

| 1 | 1 | 1 | 1   | 1                 | 1                   | l   | 1                         |

# **23. Define duality property**

Duality property states that every algebraic expression deducible from the postulates of Boolean algebra remains valid if the operators and identity elements are interchanged. If the dual of an algebraic expression is desired, we simply interchange OR and AND operators and replace 1's by 0's and 0's by 1's.

# 24. State De Morgan's theorem. (*NOV/DEC 2010*), (*APR/MAY 2010*), (*MAY/JUNE 2014*) De Morgan suggested two theorems that form important part of Boolean algebra.

1) The complement of a product is equal to the sum of the complements.

$$AB)' = A' + B'$$

2) The complement of a sum term is equal to the product of the complements.

$$\mathbf{A} + \mathbf{B})' = \mathbf{A'B}$$

#### 25. What are called don't care conditions?

In some logic circuits certain input conditions never occur, therefore the corresponding output never appears. In such cases the output level is not defined, it can be either high or low. These output levels are indicated by 'X' or'd' in the truth tables and are called don't care conditions or incompletely specified functions.

# 26. Convert the given expression in canonical SOP form Y = AC + AB + BC(NOV/DEC 2015, 2016), (APR/MAY 2016)

$$\begin{split} Y &= AC + AB + BC \\ &= AC(B + B') + AB(C + C') + (A + A')BC \\ &= ABC + ABC' + AB'C + AB'C' + ABC + ABC' + ABC \\ &= ABC + ABC' + AB'C + AB'C' \end{split}$$

- 27. Convert the given expression in canonical SOP form Y = AC + AB + BC (*NOV/DEC 16*)

- =AC(B + B') + AB(C + C') + (A + A')BC

- = ABC + ABC' + AB'C + AB'C' + ABC + ABC' + ABC

- =ABC + ABC' + AB'C + AB'C'

- **28.** Simplify  $\mathbf{F} = \mathbf{ABC} + \mathbf{AB'C} + \mathbf{A'C} + \mathbf{AB'}$

(MAY/JUNE 2014)

- F = ABC + AB'C + A'C + AB'= AC(B+B') + A'C + AB' = AC + A'C + AB'

- = C + AB'

# 29. Simplify the expression Z= AB + AB'(A'C')' (*MAY/JUNE 2016*)

- Z = AB + AB'(A'C')'

- = AB + AB'(A+C)

$$= AB + AB' + AB'C$$

$$= A (B + B' + B'C)$$

$$= A (1+B'C) = A$$

- 30. Simplify the expression Z= B' + AB'+A'C' (*NOV/DCE 2014*)

- $Z = \hat{B}' + AB' + A'C'$

= B'+A'C'

# 31. What are the different classification of binary codes?

- Weighted codes

- Non weighted codes

- Reflective codes

- Sequential codes

- Alphanumeric codes

- Error Detecting and correcting codes.

# **32. Define logic gates?**

Logic gates are electronic circuits that operate on one or more input signals to produce an output signal. Electrical signals such as voltages or currents exist throughout a digital system in either of two recognizable values. Voltage- operated circuits respond to two separate voltage levels that represent a binary variable equal to logic 1 or logic 0.

#### 33. Why are NAND and NOR gates known as universal gates?

The NAND and NOR gates are known as universal gates, since any logic function can be implemented using NAND or NOR gates.

#### 34. What is a maxterm or POS?

n variables forming an OR term, with each variable being primed or unprimed, provide 2" possible combinations, called maxterms, or standard sums.

#### 35. What is minterm or SOP?

n variables forming an AND term, with each variable being primed or unprimed, provide 2" possible combinations, called minterms, or standard products.

#### 36. What is a prime implicant? (APR/MAY 2010), (NOV/DEC 2013)

.

A prime implicant is a product term obtained by combining the maximum possible number of adjacent squares in the map. If a minterm in a square is covered by only one prime implicant, that prime implicant is said to be essential.

37. What is the value of 'b' if  $\sqrt{41_b} = 5$ ? (MAY /JUNE 2012)

The value of b = 6

**38.** Convert (108.2)10 and (10110.110)2 into hexadecimal numbers. (*APR/MAY 2011*)

$$16 \underbrace{108}_{6-6} \qquad \begin{array}{c} 0.2 \times 16 = \\ 0.2 \times 16 = \\ 0.2 \times 16 = \\ 3.2 \\ 3.2 \\ \end{array}$$

Hence,  $(108.2)_{10} = (66.222)_{16}$

00010110.1100 16 С Hence,  $(10110.110)_2 = (16.C)_{16}$ 39. Determine (377)<sub>10</sub> in octal and hexa decimal equivalent (NOV/DEC 2014)  $(377)_{10} - 571$ (i) (377)10 - 179 (ii) 40. Simplify  $X\overline{Y} + ZX\overline{Y}$ (APR/MAY 2011)  $= X\overline{Y} + ZX\overline{Y}$  $= X\overline{Y}[1+Z] = X\overline{Y}$ 41. Simplify the expression  $\overline{ABC} + BC + AC$ (NOV/DEC 2011) =ABC+BC+AC $= \left[\overline{AB} + B\right]C + AC$  $= \left[\overline{A} + B\right]C + AC$  $=\overline{AC}+BC+AC$  $=\left[\overline{A}+A\right]C+BC$

$$= C + BC = C[1+B] = C$$

42. What is the decimal equivalent of (8963)<sub>16</sub>? (NOV/DEC 2010)

Hence, (8963)<sub>16</sub>= (35157)<sub>10</sub>

#### 43. What is the abbreviation of ASCII and EBCDIC code?

- ASCII-American Standard Code for Information Interchange.

- **EBCDIC**-Extended Binary Coded Decimal Information Code.

- 44. What are the universal gates?

NAND and NOR

# 45. What are the different types of number complements?

- i) r's Complement

- ii) (r-1)'s Complement.

# **46.** Express the function f(x, y, z)=1 in the sum of minterms and a product of maxterms? Minterms=Σ(0,1,2,3,4,5,6,7)

Maxterms=Nomaxterms.

# 47. Explain or list out the advantages and disadvantages of K-map method? (MAY /JUNE 2012)

#### The *advantages* of the K-map method are

i. It is a fast method for simplifying expression up to four variables.

ii. It gives a visual method of logic simplification.

- iii. Prime implicants and essential prime implicants are identified fast.

- iv. Suitable for both SOP and POS forms of reduction.

v. It is more suitable for class room teachings on logic simplification.

#### The *disadvantages* of the K-map method are

i. It is not suitable for computer reduction.

ii. K-maps are not suitable when the number of variables involved exceed four.

iii. Care must be taken to fill in every cell with the relevant entry, such as a 0, 1 (or) don't care terms

#### 48. What is Hamming code?

#### (NOV/DEC 2013)

One of the most common error-correcting codes used in random-access memories was devised by R. W. Hamming. In the Hamming code, k parity bits are added to an *n*-bit data word, forming a new word of n + k bits. The bit positions are numbered in sequence from I to n + k. Those positions numbered as a power of 2 are reserved for the parity bits. The remaining bits are the data bits. The code can be used with words of any length.

49. State absorption theorem in Boolean algebra. (*NOV/DEC 2010*)

i.

$$x + xy = x$$

i.  $x(x+y) = x$

50. Simplify the function  $Y = \sum m(1,3,5,7)$  (*MAY/JUNE 2013*)

#### 51. What are the various digital logic families available?

#### 52. List the characteristics of digital IC family.

- Fan in

- Fan out

- Power dissipation

- Propagation delay

- Noise margin

- Speed power product

#### 53. What is totem pole configuration?

It is the output stage of a TTL gate. The name totem pole stems from the apparent stacking of one transistor on the top of another.

# 54. State the advantages and drawbacks of totem pole output.(*NOV/DEC 2013*) Advantages:

- External pull up resistor is not required

- Operating speed is very high

#### **Drawbacks:**

• Output of two gates cannot be tied together

# 55. Describe the characteristics of TTL family.

| S.No | CHARACTERISTICS   | VALUES                                                   |

|------|-------------------|----------------------------------------------------------|

| 1.   | Supply voltage    | For 74 series - (4.75 to 5.25) units                     |

|      |                   | For 54 series $-(4.5 \text{ to } 5.5)$ units             |

| 2.   | Temperature range | For 74 series $-(0^{\circ}C \text{ to } 70^{\circ}C)$    |

|      |                   | For 54 series $-(-55^{\circ}C \text{ to } 125^{\circ}C)$ |

| 3.   | Voltage levels    | V <sub>OL(max)</sub> - 0.4V                              |

|    |                   | $V_{a} \sim 2.4 V_{a}$ |

|----|-------------------|------------------------|

|    |                   | $V_{OH(min)} - 2.4V$   |

|    |                   | $V_{IL(max)}$ - 0.8V   |

|    |                   | $V_{IH(min)} - 2.0V$   |

| 4. | Noise margin      | 0.4V                   |

| 5. | Power dissipation | 10 mW per gate         |

| 6. | Propagation delay | Typically 10 ns        |

| 7. | Fan out           | 10                     |

# 56. List the sub families of TTL.

- Standard TTL

- High speed TTL

- Low power TTL

- Schottky TTL

- Low power Schottky TTL

- Advanced Schottky TTL

- Fast TTL

- Advanced Low power Schottky TTL

#### 57. How is the high speed achieved in TTL?

All the resistance values are reduced due to which high switching speed is achieved. Also a Darlington pair is provided which generates a high current gain hence power consumption is reduced.

#### 58. Give the comparison between TTL, CMOS and ECL families.

| S.no | Parameter         | TTL   | CMOS          | ECL   |

|------|-------------------|-------|---------------|-------|

| 1.   | Propagation delay | 10ns  | 70ns          | 750ps |

| 2    | Noise margin      | 0.4V  | $0.45 V_{DD}$ | 150mW |

| 3    | Power dissipation | 10mW  | 0.01mW        | 5mW   |

| 4    | Fan out           | 10    | 50            | 25    |

| 5    | Figure of merit   | 100pJ | 0.7pJ         | 0.5pJ |

- **59. Which IC family offers low propagation delay and Low power dissipation?** ECL and CMOS

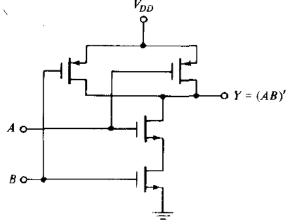

- 60. Draw the logic circuit of CMOS NAND gate (*NOV/DEC 2012*)

61. Define fan out and fan in. (*NOV/DEC 2011,2015*), (*MAY/JUNE 2016*)

**Fan in :** Maximum number of inputs that can be connected to a logic gate without any impairment of its normal operation is called as fan - in

Fan - Out: Maximum number of standard loads that output of the gate can be drive without any impairment or degradation of its normal operation

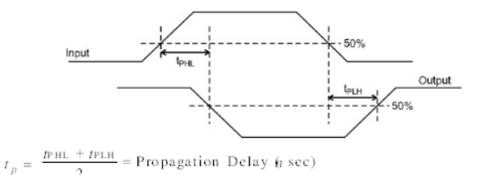

#### 62. Define propagation delay (MAY/JUNE 2014)(APRIL/MAY 2015)

Propagation delay is the average transition delay time for the signal to propagate from input to output when the signals change in value. It is expressed in ns. Propagation Delay is the maximum time taken by output to change its state in response to input. The

propagation delay determines the speed of operation of a gate. In general switching speed is measured when 50% duty cycle time square wave is applied at a input and a square wave is generated at output, The times are measured from 50% of voltage levels. The time  $t_{PHL}$  is delay when output goes LOW from HIGH and  $t_{PLH}$  is the time delay taken by output to go HIGH from LOW state. The propagation delay  $t_p$  is average of the two times and measured in n sec.

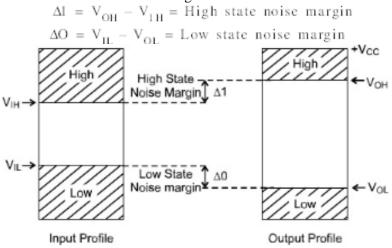

#### 63. Define noise margin. (*MAY/JUNE 2014*)

It is the maximum noise voltage added to an input signal of a digital circuit that does not cause an undesirable change in the circuit output. It is expressed in volts. Unwanted electric signals, called noise, can appear when connecting the logic devices. These noise signals can cause the voltage levels to rise or reduce from intended value. This may cause circuit malfunction. For example if noise causes an input voltage to reduce below the  $V_{1H}$ , then input is not recognized as logic 1 and thus the circuit malfunctions. The ability of a circuit to tolerate the effect of noise is called as noise immunity. The amount by which a circuit can tolerate the effect of noise is called noise margin.

#### 64. What is power dissipation?

Power dissipation is measure of power consumed by the gate when fully driven by all its inputs.

#### 65. What is power dissipation factor?

Power Dissipation  $(P_D)$  is defined as the power dissipated in an IC and measured in mW. It is desired to have low power dissipation to reduce cooling, but it may increase the propagation delays.

#### 66. What is speed power product?

Speed power product is defined as the as the product of propagation delay (in nano seconds) and power dissipation (in mW) and is measured in pico joules. It is also referred as the figure of merit of a digital IC

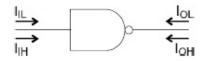

#### 67. Explain the various Input and output Currents

For a high – state gate driving a second gate,

$I_{OH}$  – high level output current, current that flows from an output in the logic – 1 state under specified load conditions

$I_{IH}$  – high level input current, current that flows into an input when a logic – 1 voltage is applied to that input.

For a low state gate driving a second gate,

$I_{OL}$  – Low level output current, current that flows from an output in the logic-0 state under specified load conditions.

$I_{IL}$  – Low level input current, current that flows into an input when a logic – 0 voltage is applied to that input.

#### 68. List the advantages and drawbacks of ECL. (APR/MAY 2010) Advantages:

- 1. Current drawn from the supply is steady

- 2. Switching time is less.

#### **Disadvantages:**

- 1. It is difficult to achieve good noise immunity

- 2. Power consumption is increased as the transistors are saturated.

#### 88. What factors limit CMOS fan -out?

The CMOS fan out depends on the permissible maximum propagation delay. For low frequencies the fan out is 50Hz, and for high frequencies it will be less.

#### 89. What can happen if TTL output is connected to more unit loads that its output rating specifications? (MAY /JUNE 2012)

If more gate inputs are specified by the fan out are connected to the output of the gate, the gate may not function correctly. Indeed even when the fan out is not exceeded, each additional load at the gate tends to increase the switching time of the gate. For high speed operations manufacturers usually recommend a maximum loading factor which is less than the dc loading capability of the gate. The limits on the fan out of the gate are caused by the currents which flow when the input has to be held at one level usually 0.

#### 90. Give the fan - in, fan - out and noise margin range of a TTL family NAND gate. (APR/MAY 2011)

| ٠ | Noise margin | = 0.4 V |

|---|--------------|---------|

| • | Fan in       | = 8     |

- Fan in

- = 10Fan out

- 91. Compare TTL, ECL, CMOS families for switching speed. (NOV/DEC 2010)

- TTL Faster than CMOS

- ECL Fastest of all

- CMOS Less than TTL

#### 92. What are the uses of a buffer? (MAY/JUNE 2013)

Buffer is used to transfer the output of the input circuit to that of the output circuit

#### 93. State advantages and disadvantages of TTL

#### Advantages:

- Easily compatible with other ICs

- Low output impedance

# **Disadvantages:**

- Wired output capability is possible only with tristate and open collector types. Special circuits in Circuit layout and system design are required.

- 94. When does the noise margin allow digital circuits to function properly?

When noise voltages are within the limits of VNA(High State Noise Margin) and VNK for a particular logic family.

**95.** What happens to output when a tristate circuit is selected for high impedance. Output is disconnected from rest of the circuits by internal circuitry.

#### 96. What is 14000 series?

It is the oldest and standard CMOS family. The devices are not pin compatible or electrically compatible with any TTL Series.

97. Convert the following binary code into a gray code 1010111000<sub>2</sub> (MAY/JUNE 2015)

#### 98. Convert (APR/MAY 2016)

- a.  $(475.25)_8$  to its decimal equivalent  $-317.328_{10}$

- b. (**549.B4**)<sub>16</sub> to its binary equivalent 0101 0100 1001. 1011 0100<sub>2</sub>

99. Compare the totempole output and open collector output (NOV/DEC 2014)

| S.No | TOTEM POLE                                                                                | OPEN COLLECTOR                                                          |

|------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 1. 1 | Output state consist of pull up<br>transistor, diode resistor and<br>pull down transistor | Output stage consists of only pull down transistor.                     |

| 2.   | External pull-up resistor is not required                                                 | External pull-up resistor is required for proper operation of gate.     |

| 3.   | Output of two gates cannot be tied together.                                              | Output of two gates can be tied<br>together using wired AND<br>tehnique |

| 4.   | Operating speed is high                                                                   | Operating speed is low.                                                 |

# 100. Convert the following Excess – 3 number into decimal numbers (NOV/DEC 2016)

- 1. 1011 8

- 2. 1001 0011 0111- 604

# PART – B

- 1. Convert the following numbers to their decimal equivalents BC2<sub>16</sub> and (11011.011)<sub>2</sub> (*APR/MAY 2010*), (*NOV/DEC 2011*), (*NOV/DEC 2012*), (*MAY/JUNE 2013*)(*NOV/DEC 2013*) (*MAY/JUNE 2016*) (*NOV/DEC 2016*) (T2-5-9)

- Binary, BCD, Octal, Hexa decimal, Excess -3 Arithmatic (APR/MAY 2015)(NOV/DEC 2015)

- 3. Prove that  $\overline{AB} + \overline{A} + AB = 0$  (*NOV/DEC 2010*) (**T2–43-44**)

- 4. Express function Y = AB + BC + AC in canonical sum of product form. (*NOV/DEC 2011*), (*NOV/DEC 2012*), (*MAY/JUNE 2013*) (*NOV/DEC 2013* (T2-44-51)

- Encode the binary word 1011 into seven bit even parity Hamming code (APR/MAY 2010), (NOV/DEC 2012) (NOV/DEC 2013) (NOV/DEC 2014) (NOV/DEC 2015) (MAY/JUNE 2015) (MAY/JUNE 2016) (NOV/DEC 2016) (T 2- 268 - 269)

- 6. Using the NOR outputs of two ECL gates, show that when connected together to an external resistor and negative supply voltage, the wired connection produces an 'OR' function (*APR/MAY 2011*) (*MAY/JUNE 2012*), (*NOV/ DEC 2012*), (*MAY/JUNE 2013*) (*NOV/DEC 2013*) (*MAY/JUNE 2016*) (T2-420-421)

- Write detailed notes on CMOS technology (MAY/JUNE 2012), (NOV/ DEC 2010) (APR/MAY 2010), (NOV/ DEC 2012), (APR/MAY 2011), (NOV/DEC 2015), (NOV/DEC 2016) (NOV/DEC 2014) (T2-423-427)

Explain the working of three input TTL Inverter, NAND totem pole output gate, NOR gates (APR/MAY 2011), (NOV/ DEC 2011), (NOV/ DEC 2010) (NOV/DEC 2013)(NOV/DEC 2014) (MAY/JUNE 2015) (MAY/JUNE 2016) (T2-410-419)

#### Unit – II COMBINATIONAL CIRCUITS

#### PART – A

# 1. What are combinational circuits?

A combinational circuit consists of logic gates whose outputs at any time are determined from the present combination of inputs. A combinational circuit performs an operation that can be specified logically by a set of Boolean functions. It consists of input variables, logic gates, and output variables.

# 2. Give the design procedures for the designing of a combinational circuit.

The procedure involves the following steps,

- From the specification of the circuit, determine the required number of inputs and outputs and assign a symbol to each.

- Derive the truth table that defines the required relationships between inputs and outputs.

- Obtain the simplified Boolean functions for each output as a function of the input variables.

- Draw the logic diagram and verify the correctness of the design.

# 3. Define half adder.

A combinational circuit that performs the addition of two bits is called a half adder. A half adder needs two binary inputs and two binary outputs. The input variables designate the augend and addend bits; the output variables produce the sum and carry

# 4. Define full adder

A combinational circuit that performs the addition of three bits is a full adder. It consists of three inputs and two outputs.

# 5. Define magnitude comparator

A magnitude comparator is a combinational circuit that compares two numbers, A and B, and determines their relative magnitudes. The outcome of the comparison is specified by three binary variables that indicate whether a>b, A = b, or A < B.

# 6. What are decoders? Give an application. (NOV/DEC 2014)

A decoder is a combinational circuit that converts binary information from n input lines to a maximum of  $2^n$  unique output lines. If the n bit coded information has unused combinations, he decoder may have fewer than  $2^n$  outputs.

The decoders are used in code converters, implementation of combinational circuits, address decoding, BCD to 7- segment decoder.

# 7. What are encoders?

An encoder is a digital circuit that performs the inverse operation of a decoder. An encoder has  $2^n$  and n output lines. The output lines generate the binary code corresponding to the input value.

# 8. Define priority encoder

A priority encoder is an encoder circuit that includes the priority function. The operation of priority encoder is such that if two or more inputs are equal to 1 at the same time, the input having the highest priority will take precedence.

# 9. Define multiplexer. Give an application. (NOV/DEC 2014)

A multiplexer is combinational circuit that selects binary information from one of many input lines and directs it to a single output line. The selection of a particular input line is controlled by a set of selection lines. Normally there are  $2^n$  input lines and n selection lines whose bit combinations determine which input is selected.

They can be used as a data selector to select one out of many data inputs, to implement combinational logic circuit, in time multiplexing systems, in frequency multiplexing systems, in data acquisition systems

- **10. What is the function of a multiplexers select inputs**?(*NOV/DEC 2012*)The selection of a particular input line is controlled by a set of selection lines. Normally there are 2<sup>n</sup> input lines and n selection lines whose bit combinations determine which input is selected

- **11. What do you mean by comparator?** A comparator is a special combinational circuit designed primarily to compare the relative magnitude of two binary numbers.

- 12. What is a look ahead carry adder?

The carry propagation time is a limiting factor on the speed with which two numbers are added in parallel. The most widely used technique employs the principle of *look-ahead* carry adder. Were in the final carry is expressed in terms of the initial carry and is designed such that it does not depend on the intermediate carry values.

13. What is positive logic system? Give an example. (APR/MAY 2011) When high voltage or more positive voltage level is associated with binary '1' and while the low or less positive level is associated with binary '0' then the system adhering to this is called positive logic.

#### 14. Define Negative Logic.

When high voltage level is associated with binary '0' and while the low level is associated with binary '1' then the system adhering to this is called negative logic

#### **15.** Give the differences between DMUX and MUX (MAY /JUNE 2012)

| ~ | one me |                                    |                                       |

|---|--------|------------------------------------|---------------------------------------|

|   | S.No   | MULTIPLEXER                        | DEMULTIPLEXER                         |

|   | 1.     | It has 2 <sup>n</sup> inputs       | it has 1 input                        |

|   | 2.     | It has 1 output                    | It has 2 <sup>n</sup> outputs         |

|   | 3.     | It is also called as data selector | It is also called as data distributor |

|   | 4.     | It is used at the input side       | It is used at the output side         |

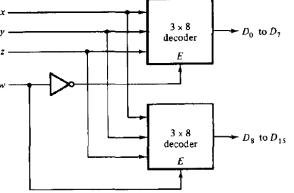

16. Draw a 4X16 decoder constructed with two 3 X 8 decoders (MAY/JUNE 2012)

17. Give the truth table of EX-OR gate. Give an example for EX-OR gate. (APR/MAY 2011) TRUTH TABLE :

| А | в | ĀB + AB |

|---|---|---------|

| O | 0 | 0       |

| 0 | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 0       |

18. Write the truth table of universal gates.(*NOV/DEC 2011*) <u>NAND GATE</u> <u>NOR GATE</u>

#### TRUTH TABLE

| А | В | A•B |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

|   |   |     |

TRUTH TABLE

| А | в | A+B |  |

|---|---|-----|--|

| 0 | 0 | 1   |  |

| 0 | 1 | 1   |  |

| 1 | 0 | 1   |  |

| 1 | 1 | 0   |  |

|   |   |     |  |

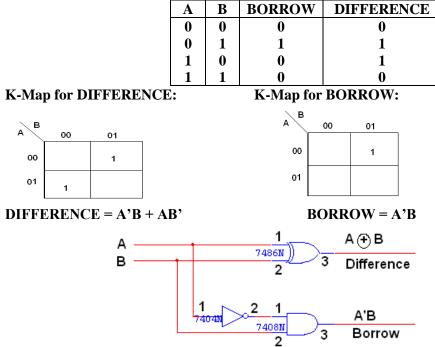

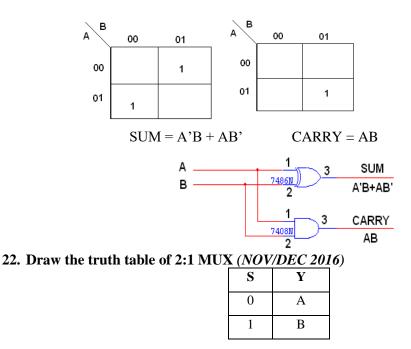

21. Design a half Adder and write its truth table. (*MAY/JUNE 2013*) TRUTH TABLE:

| Α | В | CARRY | SUM |

|---|---|-------|-----|

| 0 | 0 | 0     | 0   |

| 0 | 1 | 0     | 1   |

| 1 | 0 | 0     | 1   |

| 1 | 1 | 1     | 0   |

K-Map for SUM:

K-Map for CARRY:

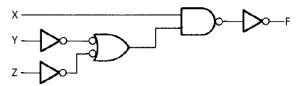

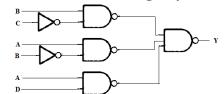

**23.** Implement the following function using only NAND gates F = (x + y) z. (*APR/MAY 2010*)

24. Implement the equation Y = BC + AB + AD using only NAND gates (MAY/JUNE 2013)

25. What is the use of enable signal? (NOV/DEC 2010)

The enable signal is used as a control signal which can be a active high or a low one depending on the application. When it is active high the circuit gets initiated and the inputs flow into the circuit only when its value is high, else the circuit gets deactivated and no out is produced. The same logic is applicable when it is a active low signal, the circuit gets activated only when it is active low and vice versa

- 26. Identify the MSI devices 74157 and 74150 (NOV/DEC 2011)

- 1. 74157 Quad 2:1 multiplexer

- 2. 74150 8:1 multiplexer

- 27. Realize the following function using NOR gates only *F*=*A*'*B*+*AB*' (*MAY/JUNE 2014*)

28. Implement the function F = A.B using NOR gates (*NOV/DEC 2013*)

29. Draw the logical diagram of EX-OR gate using NAND gates. (NOV/DEC 2015)

30. Write the POS representation of  $f(x,y,z) = \sum m (0,1,3,5,7) (MAY/JUNE 2016)$

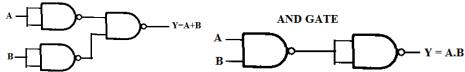

31. Construct OR gate to AND gate using NAND gate. (NOV/DEC 2016) OR GATE

32. Show how the JK flip-flop can be modified into a D flip-flop or a T flip-flop (NOV/DEC 2014) J=

# PART – B

- 1. Simplify using K-map  $F = \pi M(0, 1, 3, 6, 8, 9, 11, 15) (APR/MAY 2011) (NOV/DEC 2016)$ (T2 - 76 - 79)

- 2. Simplify the expression  $Y = \sum m(3,4,6,7,8,9,10,13,14,15)$  using K-map using logic gates (NOV/DEC 2011), (NOV/DEC 2010) (NOV/DEC 2013) (MAY/JUNE 2014) (NOV/DEC 2016) (NOV/DEC 2015) (NOV/DEC 2016) (T2-70-74)

- 3. Obtain the minimum SOP using Quine McClusky's method and verify using K map  $F = m_0 + m_2 + m_4 + m_8 + m_9 + m_{10} + m_{11} + m_{12} + m_{13}$  (MAY/JUNE 2012) (T2(2e)(112-120))

- 4. Simplify the following using Quine McClusky method. Realize the reduced function using NAND gates.  $F = \sum m (0,2,3,4,7,8,11,12,13) + \sum d(5,6)$  (APR/MAY 2011), (NOV/DEC 2011), (MAY/JUNE 2013) (NOV/DEC 2013) (MAY/JUNE 2014) (T2(2e)-112-120)

- 5. Reduce the function after identifying the essential and non essential prime implicants.  $F = A'B'C'D' + A'B'C'D + A'B'CD + A'BC'D' + A'BC'D + A'BCD \quad (NOV/DEC \ 2010),$ (APR/MAY 2010) (T2(2e) - 112 - 120)

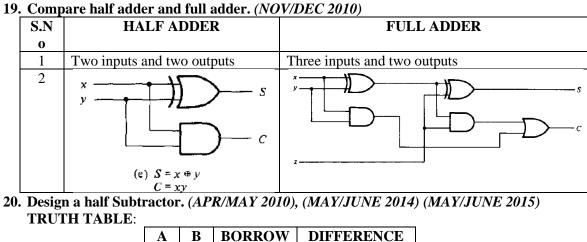

- 6. Design Half adder and Full Adder (*APR/MAY 2011*), (*APR/MAY 2010*), (*NOV/DEC 2012*) (NOV/DEC 2013) (T2-119-122)

- 7. Design a Half Subtractor and full subtractor circuit (APR/MAY 2011), (NOV/DEC 2011), (NOV/DEC 2010), (MAY/JUNE 2013) (NOV/DEC 2016) (T2-143-157)

- 8. Explain the carry look ahead adder (NOV/DEC 2010) (T2-123-126)

- 9. Design a code converter (NOV/DEC 2010), (APR/MAY 2010),(NOV/DEC 2011), (NOV/DEC 2012) (MAY/JUNE 2013) (NOV/DEC 2013) (MAY/JUNE 2014) (T2-116-118)

- 10. Design a decoder and problems (NOV/DEC 2013) (T2-134-138)

- 11. Design an encoder (**T2–139-141**)

- 12. Design and construct an eight input priority encoder (MAY/JUNE 2012) (T1-140-141)

- 13. Design a combinational circuit that will multiply two 2 bit binary values (MAY/JUNE 2012), (APR/MAY 2011) (T2-131-132)

- 14. Design a Magnitude Comparator (APR/MAY 2011), (NOV/DEC 2011), (APR/MAY 2010) (T2 - 133 - 134)

- 15. Design a demultiplexer (NOV/DEC 2011) (Bakshi text book)

- 16. Design a multiplexer (**T2–141-146**)

17. Implement the function  $F(A, B, C, D) = \sum 1,3,5,6$  using MUX (*NOV/DEC 2010*),

# (MAY/JUNE 2013), (APR/MAY 2010) (MAY/JUNE 2014) (T2-144-145)

18. Draw the logic diagram of IC 74138 and explain the operation with truth table (*NOV/DEC 2012*) (T2–175-179)

#### Unit – III SYNCHRONOUS SEQUENTIAL CIRCUITS PART – A

# 1. Define sequential circuit?

In sequential circuits the output variables dependent not only on the present input variables but they also depend up on the past history of these input variables.

# 2. What are the classification of sequential circuits?

The sequential circuits are classified on the basis of timing of their signals into two types. They are,

1)Synchronous sequential circuit.

2)Asynchronous sequential circuit.

# 3. What do you mean by present state?

The information stored in the memory elements at any given time defines the present state of the sequential circuit.

4. What do you mean by next state? The present state and the external inputs determine the outputs and the next state of the sequential circuit.

# 5. What are the types of sequential circuits?

- Synchronous sequential circuits

- Asynchronous sequential circuits

# 6. Define synchronous sequential circuit

In synchronous sequential circuits, signals can affect the memory elements only at discrete instant of time. A synchronous sequential circuit is a system whose behavior can be defined from the knowledge of its signals at discrete instants of time.

# 7. Define Asynchronous sequential circuit?

In asynchronous sequential circuits change in input signals can affect memory element at any instant of time

# 8. What is edge triggering and what are its types? (*NOV/DEC 2015*)

Flip flop change states when commanded to do so by a synchronizing clock pulse. When the flip flop changes state on the clock edge it is said to be edge triggered. Both positive and negative edge trigged flip flop are commonly available.

# 9. Define flip-flop

Flip - flop is a sequential device that normally. samples its inputs and changes its outputs only at times determined by clocking signal.

# 10. What are the applications of flip flops?

- 1. Shift registers

- 2. Counters

- 3. Sequence detector

- 4. Memory unit

- 5. Clock pulse generator

- 6. Serial adder

# **11.** List various types of flip-flop

- 1] SR latch

- 2] D latch

- 3] Clocked J.K. flip-flop

- 4] T flip-flop

# 12. What is race around condition?

In the JK latch, the output is feedback to the input, and therefore change in the output results change in the input. Due to this in the positive half of the clock pulse if J and K are both high then output toggles continuously. This condition is known as race around condition.

#### 13. What are the two models in synchronous sequential circuits.

- Moore circuit

- Mealy circuit

# 14. What is Mealy circuit? (NOV/DEC 2015)

When the output of the sequential circuit depends on both the present state of flip-flop and on the input, the sequential circuit is referred to as mealy circuit.

#### 15. What is moore circuit? (NOV/DEC 2015)

When the output of the sequential circuit depends only on the present state of the flip-flop, the sequential circuit is referred to as moore circuit.

# 16. Differentiate Mealy and Moore model (*NOV/DEC 2016*), (*MAY/JUNE 2016*)(*NOV/DEC 2014*)

| S.No | Mealy circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Moore circuit                             |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 1    | When the output of the sequential circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | When the output of the sequential circuit |

|      | depends on both the present state of flip-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | depends only on the present state of the  |